Practica 2 EdC - FSM Verilog - 24 Marzo 2014 (2)

-

Upload

diego-armando-badilla-castillo -

Category

Documents

-

view

24 -

download

1

description

Transcript of Practica 2 EdC - FSM Verilog - 24 Marzo 2014 (2)

-

DEPARTAMENTO DE TECNOLOGA INFORMTICAESCUELA TCNICA SUPERIOR DE INGENIERA INFORMTICA

Mquinas de Estados Finitos (FSM) en Verilog

Enunciados de Prcticas de LaboratorioEstructura de Computadores

v1.03

1 Introduccin y objetivos

En esta prctica nos basaremos en los conocimientos adquiridos en la prctica anterior. Por tanto, sepresupone que el alumno sabe:

Crear un proyecto en el entorno ISE de Xilinx.

Trabajar con mdulos Verilog simples, de tipo secuencial y de tipo combinacional.

Trabajar con mdulos ms complejos definidos de forma estructural mediante la interconexinde instancias de mdulos ms simples.

Usar mdulos de testbench para simular y comprobar el funcionamiento de los mdulosdiseados.

Modificar un mdulo de testbench para adaptarlo a las pruebas a las que desea someter elmdulo a probar.

Los objetivos para esta prctica son trabajar con mdulos Verilog ms complejos correspondientes ala descripcin de Mquinas de Estados Finitos (FSM). En concreto, se pretende:

Describir en Verilog de forma estructural un Circuito Secuencial Sncrono (CSS) partiendo delesquema de puertas lgicas y biestables de dicho circuito.

Describir en Verilog de forma procedimental un circuito secuencial sncrono que implemente unaMquina de Estados Finitos (FSM) utilizando como punto de partida nicamente el diagrama deestados de dicha mquina.

Usar y modificar mdulos de testbench para simular y verificar el comportamiento de losmdulos diseados.

-

Estructura de Computadores 2

Hacer uso de las herramientas de sntesis del entorno ISE de Xilinx para comprobar que a partirde la descripcin procedimental de un modulo Verilog se obtiene un circuito equivalente.

2 Estudio previo

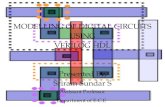

En esta prctica se va a describir en Verilog, de dos formas distintas, el Circuito Secuencial Sncrono(CSS) de la figura 1.

Figura 1: Circuito Secuencial Sncrono (CSS)

Utilizando las tcnicas de anlisis vistas en la asignatura CED podramos analizar el CSS de la figura2 y obtener el diagrama de estados de la mquina de estados finitos (FSM) que implementa. Dichodiagrama se muestra en la figura 2.

Figura 2: Diagrama de estados de la FSM

Por tanto, es fcil interpretar que el circuito de la figura 1 es capaz de detectar en la entrada 'x' unasecuencia de tres unos seguidos (con solapamiento) y, en ese momento, activar la salida 'z'.

La figura 3 nos muestra la forma general de cualquier Circuito Secuencial Sncrono (CSS).

-

Estructura de Computadores 3

Figura 3: Estructura general de un CSS

Si reorganizamos los elementos del circuito de la figura 1 para adaptarlos a la forma general de unCSS mostrada en la figura 3, obtenemos un circuito como el que se muestra en la figura 4. Ntese queen el grfico de la figura 4 no se estn mostrando todos las puertas lgicas que forman parte del circuitocombinacional, porque es tarea del alumno completarlo, como veremos ms adelante.

Figura 4: Reestructuracin de los elementos del circuito para adoptar la forma general de un CSS

-

Estructura de Computadores 4

3 Descripcin estructural de un CSS a partir del circuito

Se pretende describir en Verilog el circuito secuencial sncrono de la figura 4 y que, como sabemos,es equivalente al de la figura 1. Realizaremos una descripcin Verilog de tipo estructural, instanciando einterconectando mdulos .

Para esta parte de la prctica se dispone de los seis archivos Verilog detallados a continuacin, en latabla 1:

ARCHIVO CONTENIDO TAREA A REALIZARbiestable_JK.v Descripcin Verilog de un

biestable JK.Estudiar su funcionamiento antes de la sesin de laboratorio.

biestable_T.v Descripcin Verilog incompleta de un biestable T.

Completar la descripcin Verilog durante la sesin de laboratorio.

circuito_combinacional.v Descripcin Verilog incompleta del circuito combinacional de la figura 4.

Completar la descripcin Verilog durante la sesin de laboratorio.

circuito_secuencial.v Descripcin Verilog incompleta del circuito secuencial de la figura 4.

Completar la descripcin Verilog durante la sesin de laboratorio.

biestable_T_tb.v Descripcin Verilog del modulo de testbench del mdulo biestable_T.

Usarlo durante la sesin de laboratorio para probar que el mdulo biestable_T funciona correctamente.

circuito_secuencial_tb.v Descripcin Verilog del modulo de testbench del mdulo circuito_secuencial.

Usarlo durante la sesin de laboratorio para probar que el mdulo circuito_secuencial funciona correctamente. Modificarlo durante la sesin de laboratorio para probar nuevas secuencias de entrada.

Tabla 1

3.1 Creacin del proyecto.

Cree un proyecto en el entorno ISE, tal y como aprendi en la primera prctica, dndole el nombreque prefiera. Recuerde que no puede aparecer ningn carcter acentuado en ninguna parte de la rutade carpetas que conduce al proyecto.

Aada al proyecto, de una sola vez, los seis archivos de la tabla 1, salvo que su profesor le indiqueque debe ir aadiendo los archivos al proyecto conforme los vaya necesitando.

3.2 Descripcin Verilog del biestable T

Complete el mdulo biestable_T presente en el archivo biestable_T.v (fragmento de cdigo 1). Luegoutilice el testbench del archivo biestable_T_tb.v para comprobar que funciona correctamente. El aspectode los primeros 50 ns de la simulacin debe ser idntico al de la figura 5. Fjese bien en los resultadoscompletos de la simulacin y si cree que el biestable T que ha diseado no funciona correctamenterevise el cdigo Verilog y modifquelo hasta que est usted conforme con lo que ve en la simulacin.Cuando crea que todo es correcto conteste a las siguientes cuestiones sobre la simulacin:

1. Cmo se puede apreciar, en la simulacin, que la seal de clear (cl) es asncrona?

-

Estructura de Computadores 5

2. En que instantes (en ns) se pone a 1 el biestable?

3. En qu instantes (en ns) se pone a 0 el biestable sin que sea a causa de la seal de clear (cl)?

Para averiguar fcilmente los tiempos que se le preguntan puede hacer click sobre las formas deonda con el ratn. Esto hace que aparezca en esa posicin un cursor amarillo, como el que se ve en lafigura 5, que le informa del valor del tiempo de simulacin en ese instante. De forma similar, al hacerclick y arrastrar el ratn sobre las formas de onda aparecen dos cursores y podemos medir diferenciasde tiempo.

// Biestable T sincronizado por flancos de subida de reloj.// Tiene una seal de clear 'cl' asincrona, activa en baja.

module biestable_T( input clk, input T, input cl, // 'cl' es asincrona y activa en baja output reg q ); // Describa el funcionamiento del biestable T de forma // procedimental utilizando un bloque 'always' // ESCRIBA AQUI SU CODIGO // ESCRIBA AQUI SU CODIGO // ESCRIBA AQUI SU CODIGO

endmodule

Fragmento de cdigo 1: Contenido del archivo biestable_T.v

Figura 5: Resultado de simular el testbench biestable_T_tb

3.3 Descripcin Verilog del circuito combinacional

Complete el mdulo circuito_combinacional presente en el archivo circuito_combinacional.v(fragmento de cdigo 2) de forma que su funcionamiento corresponda al del circuito combinacional de lafigura 4. Un buen mtodo para no equivocarse en esta tarea sera dibujar primero, sobre el bloque delcircuito combinacional de la figura 4, las puertas lgicas que faltan y que hacen que su comportamientosea equivalente al de la figura 1.

Si comete algn error al describir el mdulo circuito_combinacional, el error debera detectarsecuando ejecute, ms adelante, el testbench del mdulo circuito_secuencial que, como ya se intuye en lafigura 4, va a contener una instancia del mdulo circuito_combinacional.

-

Estructura de Computadores 6

// modulo circuito_combinacional

module circuito_combinacional(

input x, input q1, input q2, output z, output T1, output J2, output K2 );

// Del esquema del circuito secuencial se ha // sacado la ecuacion de la salida 'z' y se ha // descrito con un 'assign'. assign z = x & q2;

// Saque usted de dicho esquema las ecuaciones // de excitacion de los biestables y describalas // todas con varios 'assign' justo a continuacion // ESCRIBA AQUI UN 'assign' // ESCRIBA AQUI OTRO 'assign' // ESCRIBA AQUI OTRO 'assign'

endmodule

Fragmento de cdigo 2: Contenido del archivo circuito_combinacional.v

3.4 Descripcin Verilog del circuito secuencial

En este apartado debe completar el mdulo circuito_secuencial presente en el archivocircuito_secuencial.v (fragmento de cdigo 3) de forma que su funcionamiento se corresponda con el delcircuito secuencial representado en la figura 4.

Dispone del esquema de la figura 7 para facilitarle el trabajo. En dicho esquema se muestran las tresinstancias de mdulos que forman parte del mdulo circuito_secuencial. La figura 7 muestra, para evitarerrores, los nombres de todos los elementos (los mdulos, las instancias, los puertos de entrada y desalida de los mdulos y los cables necesarios) de manera idntica a como aparecen en las diferentesdescripciones Verilog que estamos manejando.

Cuando haya terminado de modificar el archivo circuito_secuencial.v utilice el testbench del archivocircuito_secuencial_tb.v para comprobar que el mdulo circuito_secuencial funciona correctamente. Elaspecto de la simulacin durante los primeros 150 ns debe ser el de la figura 6. Si la respuesta delcircuito a las formas de onda generadas por el testbench no es la adecuada, sin duda es porque hacometido algn error en este mismo apartado o bien en el apartado anterior (el del mdulocircuito_combinacional), por lo que tendr que averiguar en qu se ha confundido y solventar el error.

-

Estructura de Computadores 7

// modulo circuito_secuencial//// Definido de forma estructural, mediante la interconexion// de instancias de otros modulos previamente definidos.

module circuito_secuencial( input clk, input x, input clear, output z );

// Cables necesarios para unir las instancias // de los dos biestables y del circuito combinacional wire cable_T1_T, cable_J2_J, cable_K2_K, cable_q_q1, cable_q_q2; // Instancia del modulo biestable_JK biestable_JK instancia_biestable_JK( .clk(clk), .J(cable_J2_J), .K(cable_K2_K), .cl(clear), .q(cable_q_q2) );

// Instancia del modulo biestable_T // ESCRIBA AQUI SU CODIGO // ESCRIBA AQUI SU CODIGO // ESCRIBA AQUI SU CODIGO

// Instancia del modulo circuito_combinacional // ESCRIBA AQUI SU CODIGO // ESCRIBA AQUI SU CODIGO // ESCRIBA AQUI SU CODIGO

endmodule

Fragmento de cdigo 3: Contenido del archivo circuito_secuencial.v

Figura 6: Primera parte del resultado de simular el testbench circuito_secuencial_tb

Si piensa que los resultados de la simulacin del mdulo circuito_secuencial_tb son correctos,conteste a las siguientes preguntas:

1. El testbench del archivo circuito_secuencial_tb.v inyecta al mdulo circuito_secuencial unasecuencia de ceros y unos sincronizada con el reloj. Cul es la secuencia completa dgitosbinarios que est generando el mdulo de testbench en la entrada 'x' para probar si funcionacorrectamente el circuito secuencial?

2. Cuntos pulsos de nivel alto aparecen en la salida 'z' del circuito_secuencial en respuesta a lasecuencia de entrada? Cunto dura cada pulso (en ns)?

3. Habra sido la salida 'z' distinta si el circuito detector de la secuencia 111 estuvieseprogramado para detectar dicha secuencia de entrada pero sin solapamiento? Indique cmohabran sido los pulsos que habran aparecido en la salida 'z' para este mismo testbench.

-

Estructura de Computadores 8

Figura 7: Esquema del mdulo circuito_secuencial utilizando nombres Verilog

3.5 Modificacin del testbench del circuito secuencial

Modifique el testbench del archivo circuito_secuencial_tb.v (fragmento de cdigo 4) para comprobarque el modulo circuito_secuencial funciona correctamente cuando recibe la secuencia de entrada001110111101111100110. Tenga en cuenta que la parte inicial de esa secuencia ya la est generandoel testbench actual. Tan solo debe aadir al final del archivo de testbench el cdigo necesario paragenerar los ltimos bits de la secuencia (los nuevos). Si lo hace correctamente, al ejecutar la nuevasimulacin sta debe durar 450 ns y el aspecto de la ltima parte debe ser el de la figura 8. Cuando creaque los resultados de la nueva simulacin son correctos, conteste a las siguientes preguntas sobre ella:

1. En que instante de tiempo (en ns) termina el pulso de mayor duracin (de nivel alto) que seaprecia en la salida 'z'?

2. Habra cambiado la forma de onda de la salida 'z' si el ltimo pulso de nivel alto de la entrada'x' hubiese durado 50 ns en lugar de 40 ns? Si es as, indique qu forma habra tenido la salida.

Figura 8: La parte final de la simulacin del mdulo circuito_secuencial_tb, tras las modificaciones

-

Estructura de Computadores 9

`timescale 1ns / 1ps

// Modulo de testbench del modulo circuito_secuencial

module circuito_secuencial_tb;

// datos 'reg' para conectar a las entradas del modulo a probar reg tb_clk; reg tb_x; reg tb_clear;

// datos 'wire' para conectar a las salidas del modulo a probar wire tb_z;

// Instancia del modulo a probar circuito_secuencial instancia_circuito_secuencial ( .clk(tb_clk), .x(tb_x), .clear(tb_clear), .z(tb_z) );

always begin // always: Siempre generando reloj de periodo 20ns #10; // espero 10ns ... tb_clk = ~tb_clk; // ...y ahora invierto la seal de reloj end initial // initial: solo se ejecuta una vez al inicio begin

tb_clk = 0; tb_x = 1'bZ; // Inicialmente 'x' est desconectada (alta impedancia = Z) tb_clear = 1; // Empiezo con el 'clear' asincrono DES-activado. #5; tb_clear = 0; // Activo 'clear' asincrono poco antes del primer flanco de subida. @(posedge tb_clk); @(posedge tb_clk); tb_clear = 1; // DES-activo 'clear' justo despus de flanco subida.

// Generacin se la secuencia de entrada. tb_x = 0; repeat (2) // x=0 durante 2 ciclos. @(posedge tb_clk);

tb_x = 1; repeat (3) // x=1 durante 3 ciclos. @(posedge tb_clk);

tb_x = 0; repeat (1) // x=0 durante 1 ciclo. @(posedge tb_clk);

tb_x = 1; repeat (4) // x=1 durante 4 ciclos. @(posedge tb_clk);

tb_x = 0; repeat (1) // x=0 durante 1 ciclo. @(posedge tb_clk);

// ESCRIBA AQUI EL NUEVO CODIGO PARA // GENERAR NUEVAS SECUENCIAS DE ENTRADA // AL CIRCUITO SECUENCIAL.

$finish; end

endmodule

Fragmento de cdigo 4: Contenido del archivo de testbench circuito_secuencial_tb.v

-

Estructura de Computadores 10

4 Descripcin Verilog de una FSM a partir del diagrama de estados

Se pretende describir en Verilog la maquina de estados finitos (FSM) cuyo diagrama de estados semuestra en la figura 2. Esta descripcin debe comportarse, como es lgico, de forma idntica al circuitode la figura 4, pero no la vamos a obtener como hemos hecho anteriormente, a partir de dicho circuito,sino que vamos a obtener el cdigo Verilog directamente, a partir del diagrama de estados, usando latcnica explicada en el tema 1 de EdC.

Para esta parte de la prctica se dispone de los archivos Verilog que a continuacin se detallan en latabla 2:

ARCHIVO CONTENIDO TAREA A REALIZARfsm.v Descripcin Verilog incompleta de la

mquina de estados (FSM) cuyo diagrama de estados se muestra en la figura 2.

Completar la descripcin Verilog durante la sesin de laboratorio.

fsm_tb.v Descripcin Verilog del mdulo de testbench del mdulo fsm.

Usarlo durante la sesin de laboratorio para probar que el mdulo fsm funcionacorrectamente.

Tabla 2

4.1 Aadir los nuevos archivos al proyecto.

Aada al proyecto que ya tiene creado los dos archivos de la tabla 2. Tenga en cuenta que es normalque le aparezcan errores de sintaxis en el panel de Consola y en el panel de Errores, pues el archivofsm.v est incompleto.

4.2 Descripcin procedimental en Verilog a partir del diagrama de estados

Complete el modulo fsm presente en el archivo fsm.v (fragmento de cdigo 5) de forma querepresente el funcionamiento de una mquina de estados finitos con un diagrama de estados como el dela figura 2 (recuerde la tcnica vista en el tema 1 de EdC)

Utilice el testbench del archivo fsm_tb.v para comprobar que el mdulo fsm funciona correctamente.

El testbench fsm_tb le est suministrando la secuencia de entrada 001110111101111100110 almdulo fsm y el comportamiento de dicho mdulo debe ser el mismo que tendra el mdulocircuito_secuencial pues debe recordar que el diagrama de estados del que hemos partido (el de lafigura 2) lo obtuvimos analizando el circuito secuencial de la figura 1. Si observa un comportamientodiferente en el mdulo fsm es debido a algn fallo en la descripcin procedimental. En ese caso, revisecon cuidado lo que ha hecho hasta encontrar el error y arreglarlo.

Si la simulacin es correcta conteste a las siguientes preguntas:

1. En que instantes (en ns) se producen flancos de subida en la salida 'z' del mdulo fsm?

2. En qu instante empieza (en ns) y cuanto dura (en ns) el pulso de nivel alto de mayor duracinque genera el mdulo de testbench en la entrada 'x'?

-

Estructura de Computadores 11

// Modulo fsm

// Descripcion procedimental en Verilog de// una maquina de estados (FSM) obtenida de// forma directa a partir de su diagrama de estados.

module fsm( input x, output reg z, input clk, input clear // El 'clear' es asincrono y activo en baja. ); reg [1:0] current_state, next_state; // Complete la declaracion de los estados. parameter A = // RELLENE LO QUE FALTA // RELLENE LO QUE FALTA // RELLENE LO QUE FALTA // Bloque 'always' para generar 'current_state' always @ ( ) // RELLENE LA LISTA DE SENSIBILIDAD if (clear==0) current_state

-

Estructura de Computadores 12

Las herramientas o procesos de sntesis estn disponibles en la vista de implementacin, dentro delpanel de diseo, por lo que debe seleccionar ahora dicha vista, de implementacin, tal como muestrala primera flecha de la figura 9.

Figura 9: Pasos a seguir para ver el esquema grfico del Top Module

Las herramientas o procesos de sntesis solo pueden aplicarse al Top Module de nuestroproyecto, es decir, al mdulo de nivel ms alto, que es el que contiene a otros mdulos y no estcontenido en ningn otro. Como nuestro proyecto tiene dos mdulos con esas caractersticas, el TopModule actual no es el que nosotros queremos, as que tendremos que hacer click con el botn derechodel ratn sobre el mdulo fsm y seleccionar en el men contextual la opcin Set as Top module paraconvertirlo en Top Module. Al hacerlo nos saldr un mensaje de advertencia como el de la figura 10 alque debemos responder Yes. Si lo hacemos bien, el mdulo fsm aparecer con un icono especfico a suizquierda, indicando que es el Top Module de nuestro diseo, tal y como indica la segunda flecha de lafigura 9.

El siguiente paso es lanzar el proceso View RTL Schematic. Para ello, habiendo seleccionado con unclick de ratn el mdulo fsm en la jerarqua de mdulos de la vista de implementacin, nos iremos a la

-

Estructura de Computadores 13

parte de abajo del panel de diseo, al subpanel de procesos, y desplegaremos la ramaSynthesize - XST, que nos mostrar el proceso View RTL Schematic. Ejecutamos (Run) el proceso conun doble click del ratn, tal y como indica la tercera flecha de la figura 9 y nos aparecer el cuadro dedilogo de la figura 11, en el que debemos marcar la opcin Start with a schematic of the top-levelblock y pulsar OK. Si todo va bien se nos habr abierto una nueva ventana llamada fsm (RTL1) comola marcada con la cuarta flecha de la figura 9 en la que podremos ver el esquema de nivel RT (RTL) delmdulo fsm, de momento representando nicamente sus puertos de entrada y de salida.

Figura 10: Confirmamos que queremos cambiar el Top Module del proyecto

Figura 11: Confirmamos que queremos empezar viendo el esquema del mdulo de ms alto nivel

Haciendo doble click sobre recuadro que representa el mdulo fsm se nos abre un nuevo esquemamostrando ms detalles sobre el funcionamiento interno de ese mdulo. Seguramente tengamos quehacer uso de los iconos que regulan el zoom ( Zoom In, Zoom Out y Zoom to Full View) parapoder ver el esquema en su totalidad (de forma anloga a como se haca en el simulador ISim para verlas formas de onda al tamao adecuado).

Si continuamos haciendo doble click varias veces sobre los nuevos mdulos que nos van apareciendo(ajustando siempre el zoom en cada esquema) llegaremos a un punto en el que no podremos adentrarnosms y en el que veremos el diseo a nivel RT (RTL) del circuito que las herramientas de sntesis hanobtenido a partir de la descripcin Verilog del mdulo fsm.

-

Estructura de Computadores 14

El esquema de ese circuito es como el mostrado en la figura 12 y en l se aprecian algunas puertaslgicas y un par de biestables, interconectados formando un circuito secuencial sncrono (CSS).

Ntese que si queremos anular un doble click hecho sobre un mdulo del esquema y volver atrs, alesquema anterior, podemos hacerlo pulsando el icono Previous Schematic o bien usando la opcindel men View > Previous Schematic

Figura 12. Circuito equivalente a la descripcin procedimental en Verilog del mdulo fsm

Un anlisis cuidadoso del circuito de la figura 12 nos revelara que si bien es cierto que el diagramade estados de la mquina de estados que implementa dicho circuito es idntico al de la figura 2, vemosque la herramienta de sntesis se ha tomado la libertad de cambiar la asignacin de cdigos efectuada alos diferentes estados de la mquina. Ha utilizado los cdigos binarios 00, 01 y 11 para los estados A, B yC en lugar de los cdigos binarios 00, 01 y 10, que son los que seguramente haya usted usado en elmdulo fsm del archivo fsm.v. El motivo de esto es, simplemente, que la herramienta de sntesis intentaobtener un circuito funcionalmente equivalente al descrito, pero adems pretende cumplir ciertoscriterios de optimizacin (de coste, velocidad, etc.) que aunque no le hayamos indicado expresamente,estn ah. Es para satisfacer esos criterios de optimizacin por lo que que a veces la herramienta desntesis hace cosas como la que estamos comentando.

1 Introduccin y objetivos2 Estudio previo3 Descripcin estructural de un CSS a partir del circuito3.1 Creacin del proyecto.3.2 Descripcin Verilog del biestable T3.3 Descripcin Verilog del circuito combinacional3.4 Descripcin Verilog del circuito secuencial3.5 Modificacin del testbench del circuito secuencial

4 Descripcin Verilog de una FSM a partir del diagrama de estados4.1 Aadir los nuevos archivos al proyecto.4.2 Descripcin procedimental en Verilog a partir del diagrama de estados4.3 Circuito equivalente a la descripcin procedimental de la FSM