La nueva canción de Chile_ T.L.Vladimirskaya, S.N (119 pags)

CENIDET · 2020. 7. 7. · S.E.P S.E.1.T S.N.1.T CENTRO NACIONAL DE INVESTIGACI~N Y DESARROLLO...

Transcript of CENIDET · 2020. 7. 7. · S.E.P S.E.1.T S.N.1.T CENTRO NACIONAL DE INVESTIGACI~N Y DESARROLLO...

S.E.P. S. E. I. T. D.G.I.T.

~

CENTRO NACIONAL DE INVESTIGACIÓN Y DESARROLLO TECNOLÓGICO

cenidet

“Nuevo convertidor ca-cd que procesa menos del 100% de la energía”

.r .$ T E S I S QUE PARA OBTENER EL GRADO DE: MAESTRO EN CIENCIAS EN INGENIERIA ELECTR~NICA P R E S E N T A : RENÉ OSORIO SANCHEZ

DIRECTORES DE TESIS: 0 1 - 0 7 3 1

M.C. NIMROD VÁZQUEZ NAVA DR. JAIME E. ARAU ROFFIEL

CUERNAVACA, MOR DICIEMBRE 2001

S.E.P S.E.1.T S.N.1.T

CENTRO NACIONAL DE INVESTIGACI~N Y DESARROLLO TECNOL~GICO

cenidet ACADEMIA DE LA MAESTR~A EN ELECTR~NICA

FORMA R11 ACEPTAClON DEL TRABAJO DE TESlS

Cuernavaca, Mor. 2001-1 1-27

Dr. Jesús Amoldo Bautista Corral üircctor del cenidet Presente

At’ii: Dr. Luis Gerardo Vela Valdés Jefe del Depto. de Electrónica

Ucsliiiis dc Iiabcr rcvisado ;I trabajo dc tesis littilado: “Nuevo conveilidor cn-cd que proces:i menos del 100’%0 de la energía”, elaborado por el aluiniio: René Osorio Shncliez, y dirigido por el M.C1 Nimrod Visquez Nava y el Dr. Jaime Eugenio Arau RoFfiel, el trabajo presentado se ACEPTA para proceder a su impresióii.

r -

cenidet INTERIOR INTERNADO PALMIRA SIN C.P. 62490 CUERNAVACA. MOR. A.P. 5.164. C.P. 62050, Cuernavaca Mor.. M6xIco

’

Tels. (73) 18-77-41 y 12-76-13. Fax. 12-24-34 Dr. Luis Gerardo Vela Valdésl Jefe del Depto de Electrónica EMAIL: [email protected]

&:

Centro Nacional de Investigación y Desarrollo Tecnológico Departamento de Electrónica

Cuemavaca, Morelos 2001-1 1-27

Ing. René Osorio Sánchez Candidato al grado de Maestro en Ciencias En Ingeniería Electrónica Presente ., Después de haber sometido a revisión su trabajo final de tesis titulado: “Nuevo convertidor ca- cd que procesa menos del 100% de la energía”, y habiendo cumplido con todas las indicaciones que el jurado revisor de tesis le hizo, le comunico que se le concede autorización para que proceda a la impresión de la misma, como requisito para la obtención del grado.

Reciba un cordial saludo. b -

A T E N T A M E N T E

Dr. Luis Gerardo Vela Valdés Jefe del Depto. de Electrónica :z--

C.C.P. expediente

cenidet Interior Internado Polmira S I N . Col. Palmira, Cvernavaca 62490, Mor.. México Apartado Postal N o . 5-164, Cuernavaca 62050. Mor., México Tels. y Fax : (73) 12-23-14. 18-77-41. 12-24-34 Dr. Dr. Luis Gerardo Velo Valdés I Jefe de Deportamento E-mail: [email protected]

y www.cenidet.edu.mx

DEDICO ESTE TRABAJO:

A Dios pues nunca me han abandonado. A m i s padres: René y Carmen. A m i s hermanos: Yselita y Alexis.

?

AGRADEZCO:

A m i s directores de tesis, al M.C. Nimrod Vázquez y a su esposa la M.C. Claudia Hernández por su apoyo y amistad. Al Dr. Jaime Arau pues su apoyo fue de gran importancia desde antes que iniciara mis estudios de postgrado, asimismo agradezco la confianza que me concedió.

A mis revisores de tesis el M. C. Rodolfo Echavarria, el Dr. Mario Ponce y el Dr. Abraham Claudio, por sus invaluables comentarios, los cuales contribuyeron a mejorar este trabajo.

A mis amigos y compañeros de generación, en orden aleatorio: Arturo Mata, Macedonio Andrés, Jesús Mina, Raúl Jiménez, Irene Guerrero, Roger Carrillo, Miguel Zapata, Luis Neri, Omar Castañeda, Miguel Mijangos. A mis amigos y compañeros en general: Antonio Cruz, Victor Moo, Andrea Cruz, Sergio Pinto, Rafael Gonzáles, Ciro Núñez , Sinuhé Ramirez, Jesús Aguayo, Horacio Visairo ...

A todo el personal del cenidet, especialmente a la Sra. Maria Elena, Srta. Angeles Canel, Ing. Jaime Rosas y al Dr. Alejandro Palacios.

Al CONACYT por el apoyo económico que me brindaron

A toda las personas del cenidet que siempre me apoyaron moralmente, muchas gracias.

TABLA DE CONTENIDO

c -4

Simbología. Lista de figuras y tablas. introducción.

CAPÍTULO 1

ESTADO DEL ARTE

1.1. introducción. 1.2. Panorama general. 1.3. Esquemas propuestos en la literatura.

1.3.1. Convertidores ca-cd tradicional con dos etapas. 1.3.2. Convertidores ca-cd con una etapa de procesamiento de la energía. 1.3.3. Convertidores ca-cd que procesa menos del 100% de la energía.

1.4.1. Planteamiento general. 1.4.2. Etapa de potencia. 1.4.3. Objetivos.

1.4. Solución propuesta.

CAPÍTULO 2

DE LA SOLUCI~N PROPUESTA TEORíA DE OPERACIÓN Y ANÁLISIS TEÓRICO

2.1. introducción. 2.2. Obtención del diagrama esquemático. 2.3. Ecuaciones y formas de ondas esperadas.

2.3.1. Pre-regulador (convertidor cd-cd elevador bidireccionai en comente). 2.3.2. Regulador (convertidor cd-cd flyback).

2.4. I. Especificaciones del convertidor propuesto. 2.4.2. Pre-regulador. 2.4.3. Regulador.

2.4. Aspectos de diseño de la etapa de potencia.

2.5. Aplicaciones del convertidor propuesto.

CAPÍTULO 3

3.1. Introducción. 3.2. Estrategia de control.

3.2.1. Condiciones de operación. 3.2.2. El control por modos deslizantes.

3.3. Modelo del sistema.

5-1 F-1 I- 1

1 2 2 3 7 9

12 11 11 12

13 13 19 19

26 29 29 30 32 34

37 37 37 39 41

? .-

I

3.3.1. Diagrama esquemático. . '

3.3.2. Circuito equivalente general. 3.3.3. Modelo matemático cuando u1'= u2 = 1. 3.3.4. Modelo matemático cuando u! = u2 = -1. 3.3.5. Modelo matemático cuando u1 = 1, u2 =.-l . 3.3.6. Modelo matemático cuando u1 = -1, u2 = 1. 3.3.7. Modelo final.

3.4. Superficie de deslizamiento. 3.5. Existencia del modo de deslizamiento. 3.6. Estabilidad dentro de la superficie de deslizamiento. 3.7. Implementación fisica. 3.8. Referencias para la etapa de control. 3.9. Limitadores de frecuencia.

I

CAPÍTULO 4

4.1. Introducción. 4.2. Prototipo desarrollado. 4.3. Simulaciones de la topología' propuesta.

4.3.1. Tensión presente en la línea ca (VLínea(t)) y corriente demandada a la línea ca (ILinea(t)). 4.3.2. Tensión rectificada de la línea de ca (Vin(t)) y tensión de salida Cvm 4.3.3. Cambio de carga. 4.3.4. Efecto de las variaciones de la tensión presente en la línea de ca (vLi",,(t)). 4.3.5. Mínimo valor del capacitor de salida (Cb) del pre-regulador.

4.4.1. Voltaje de línea y Corriente de línea. 4.4.2. Voltaje rectificado de la línea de cay voltaje de salida. 4.4.3. Cambio de carga. 4.4.4. Eficiencia.

4.4. Resultados experimentales.

4.5. Comparación de la topología propuesta con otros esquemas.

Conclusiones. Referencias. Apéndice A. Programas de simulación (simnon),

41 41 42 43 44 44 45 46 48 48 49 50 51

54 54 55 56

57

57 58

58 59 59 59 60 60 60

c- 1 R- 1 A- 1

SIMBOLOGIA C

CO ca

c b

AV AI

ex[, ex2, f

Capacitor Canacitor voluminoso para almacenamiento de energía capacitor de salida defregulador Corriente alterna Corriente directa Ciclo de trabajo Ciclo de trabajo máximo Ciclo de trabajo minimo Diodo n-esimo Rizo de tensión Rizo de corriente Tiempo de almacenamiento Tiempo muerto Variables de error: variables de estado menos referencias Frecuencia de conmutación Factor de potencia Eficiencia Eficiencia global de dos convertidores con una configuración en cascada típica Eficiencia del pre-regulador Eficiencia del regulador Eficiencia de un convertidor Reductor Eficiencia de un convertidor Reductor con dos entradas Eficiencia total Eficiencia de la etapa rectificadora Corriente de entrada del regulador en función del tiempo Valor promedio de IFei]t(t) Corriente de entrada del pre-regulador en función del tiempo Valor promedio de ILH(t) Valor eficaz de ILH(t) Corriente demandada a la línea de ca en función del tiempo Valor promedio de ILinea(t) Corriente rectificada demandada a la línea de ca en función del tiempo Valor promedio de I,"(t) Valor máximo de I,,,(t) Corriente en la carga en función del tiempo Valor promedio de I,(t) Corriente de salida del pre-regulador en función del tiempo Valor promedio de Iap(t) Corriente de salida del regulador en función del tiempo Valor promedio de IOr(t) Fracción de la energía total Inductor Inductor del convertidor Flyback Inductor del convertidor Elevador bidireccional en corriente Limitador de frecuencias Relación de vueltas del transformador

ex3, ex4

MCC Modo de conducción continua MI, Interruptor de estado sólido n-esimo

s-1

6 SMC

TC THD

Angulo de conducción entre ILilica(t) y VLinea(t) Potencia consumida en la carga Potencia liberada directamente a la carga Potencia de entrada de la topología propuesta Potencia de entrada del regulador Potencia de entrada del pre-regulador Potencia de salida del pre-regulador Potencia de salida del regulador Potencia entregada por el pre-regulador a la carga Potencia entregada directamente a la carga por la red eléctrica Potencia de entrada de la etapa rectificadora Potencia de salida de la etapa rectificadora Resistencia de carga Superficie de deslizamiento Derivada de la superficie de deslizamiento Control por modos deslizantes, por sus siglas en inglés Parámetros del controlador Período Período de conmutación Distorsión armónica total, por sus siglas en inglés Transformador n-esimo Tiempo de encendido Tiempo de apagado Control equivalente Ley de control n-esimo, interruptor ideal Ley de control real Tensión en ei capacitor voiuminoso cb en función del tiempo Valor promedio de V,b(t) Tensión de salida del regulador en función del tiempo Valor promedio de Vc,(t) Tensión rectificada de la línea de ca en función del tiempo Valor máximo de Vi,(t) Valor mínimo de Vin(t) Valor efectivo de Vin(t) Valor promedio de Vi,,(t) Tensión de salida del pre-regulador en función del tiempo Valor promedio de VOp(t) Tensión presente en la línea de ca en función del tiempo Valor promedio de Vlí,,,(t) Tensión n-esima en función del tiempo Valor promedio de V,(t) Tensión en la carga en función del tiempo Valor promedio de V,(t) Tensión de salida del pre-regulador en función del tiempo Valor promedio de Vo,(t) Frecuencia natural Variables de estado Derivadas de las variables de estado

s-2

LISTA DE FIGURAS Y TABLAS Capítulo 1

Figura 1.1

Figura 1.2

Figura 1.3

Figura 1.4 ?-

Figura 1.5

Figura 1.6

Figura 1.7

Figura 1.8

Figura 1.9

Figura 1.1 O

Figura 1.1 1

Figura 1.12

Figura 1.13

Figura 1.14 F --

Figura 1.15 Figura 1.16

Capítulo 2

Diagrama de bloques de un convertidor ca-cd con dos etapas en cascada con capacidad de corrección del FP y buena respuesta dinámica pero con baja T ~ T .

Diagrama de bloques de un convertidor ca-cd con un regulador muy eficiente, de la referencia [l]. Diagrama esquemático de un convertidor ca-cd con un regulador muy eficiente, de la referencia [l]. Modificaciones del convertidor TIBuck para estimar su eficiencia, (a) estructura básica, (b) modificaciones en las fuentes de alimentación y en la carga, (c) estructura final. Diagrama de bloques de un convertidor ca-cd con un regulador muy eficiente, de la referencia [2]. Diagrama esquemático de un convertidor ca-cd con un regulador muy eficiente, de la Diagrama de bloques de las topologías presentadas en las referencias [3-51. Diagrama esquemático de las topología presentada en la referencia

Diagrama de bloques del convertidor presentado en las referencias

Diagrama esquemático del convertidor presentado en la referencia

Topología presentada en [8-91, (a) Diagrama de bloques, (b) ángulo de conducción 4 ~ . Diagrama esquemático del convertidor presentado en la referencia

Diagrama de flujo de manejo de energía en un convertidor ca-cd, (a) procesa el 100% de la energía, (b) procesa el 200% de la energía, (c) procesa menos del 100% de la energía. Convertidor ca-cd que procesa menos del 100% de la energía, (a) diagrama de bloques, (b) circuito simplificado, (c) diagrama de bloques con capacitor de almacenamiento. Diagrama de bloques del convertidor propuesto. Diagrama esquemático del convertidor propuesto.

referencia [2].

[31.

[6-71.

[61.

PI.

2

10

11 11

Figura2.1

Figura 2.2

Diagrama de bloques de un convertidor ca-cd que procesa menos del 100% de la energía, con una etapa de conversión, Diagrama de bloques de un convertidor ca-cd que procesa menos del 100% de la energía, con dos etapas de conversión.

14

14

F- 1

Figura 2.3

Figura 2.4

Figura 2.5

Figura 2.6 Figura 2.7 Figura 2.7 Figura 2.9

Figura 2.10 Figura 2.1 1 Figura 2.12 Figura 2.13 Figura 2.14 Figura 2.15 Figura 2.16 Figura 2.17

Figura 2.18 Figura 2.19 Figura 2.20 Figura 2.21 Figura 2.22 Figura 2.23 Figura 2.24 Figura 2.25 Figura 2.26

F

Capítulo 3

Figura 3.1

Figura 3.2

Figura 3.3 Figura 3.4 Figura 3.5 Figura 3.6 Figura 3.7 Figura 3.8

*

Trahsfomiaciones de la topología propuesta (a) Diagrama eléctrico simplificado del convertidor 'propuesto, (b) diagrama eléctrico con las sustituciones de las fuentes ideales Vi y Vz por las fuentes Vi,(t) y Vc,(t) respectivamente. Diagramas de bloques y esquemático de la topologia propuesta, (a) bloques, (b) esquemático. Diagramas de bloques y de flujo de la topología propuesta donde se 'considera el efecto de la energía entregada por el pre-regulador a la carga, (a) de bloques, (b) de flujo . (a) Gráfica de q~ vs k, (b) gráfica de VT vs P, . (a) Puehte de diodos, (b) Circuito equivalente para un semiciclo. Diagrama esquemático del pre-regulador. (a ) Formas de onda del preiregulador cuando ILli(t) es positiva, (b) formas de onda del prc-regulador cuando I,-ll(t) es negativa. Gráfica de VOp(t)/V;"(t) contra D. Gráfica de la tensión de entrada del pre-regulador (Vin(t)). Gráfica del ciclo de trabajó (D) esperado en el pre-regulador. Diagrama de bloques de la topología propuesta. Corriente de entrada del pie-regulador. Balance de potencias en eli pre-regulador. Diagrama csqiiciiihtico del rcguiador. Formas dc onda del rcgulador para un ciclo de coiiiiiulacióii

Gráfica de las ganancia en tensión del convertidor Flyback. Diagrama de bloques del regulador en sene con V;"(t) y la carga. Tensión de salida del convertidor Flyback. Ciclo de trabajo D del convertidor Flyback. Gráfica de qci vs RLH. Gráfica de qc2 vs RLF. Gráfica.de q~ vs RLF y RLH. Aplicación de la topología propuesta a sistemas distribuidos. Aplicación de la topología propuesta a un sistema de iluminación basado en balastros electrónicos.

.

completo. I

1

(a) Diagrama esquemático del pre-regulador, (b) Corriente demandada por el pre-regulador. (a) Diagrama de bloques del regulador, (b) voltaje entregado por el regulador. Plano de fase para a. Plaiio de fase para -a. Plano de fase con el SMC, Diagrama Esquemático cdiiipleto de la íopología propuesta. Circuito cquivaletite dc la topología propuesia. Circuito cquivalciiic cuaiiüo u , = ui = 1.

'

I

I

I

15

15

18

18 18 20 20

22 22 23 24 24 24 26 26

27 28 28 28 31 33 34 35 35

38

38

39 40 40 41 42 42

F-2

Figura 3.9 Figura 3.10 Figura 3.1 1 Figura 3.12 Figura 3.13 Figura 3.14 Figura 3.15 Figura 3.16 Figura 3.17

Figura 3.18 Diagrama del LF.

Capítulo 4

Circuito equivalente cuando U I = U:, = -1. Circuito equivalente cuando u1 = 1, u2 = -1. Circuito equivalente cuando u! = -1, u2 = 1. Diagrama de bloques del SMC. Diagrama esquemático del SMC. Diagrama esquemático del SMC, emulador de error en corriente. Concepto de banda de histéresis para limitar la frecuencia. Concepto de retardo para limitar la frecuencia. Concepto de tiempo de encendido constante para limitar la frecuencia.

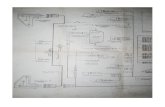

Figura 4.1 Figura 4.2 Figura 4.3 Figura 4.4

Figura 4.6.

Figura 4.7 Figura 4.8 Figura 4.9

Figura 4.1 O Figura 4.1 1 Figura 4.12 Figura 4.13

Figura 4.14

Figura 4.15

Tabla 4.1 Tabla 4.2

Diagrama del circuito implementado. Graficas a potencia nominal (100W) de: (a) VLinea(t), (b) ILinea(t). Graficas a potencia nominal (100W) de: (a) Vi,(t), (b) Vo(t). Cambio de carga de 40W a 80W, se muestran las variables: corriente en la carga I<,(t), corriente de línea Iunea(t), tensión de salida V,(t) . Cniiiportaniiento dc In topología propticsta ante variaciones dc &20Y0 de Vl,l,,,,(i), se iiiiiesiraii la tensichi ciiircgada a la Carga (V,(t)) y la corriente demandada a la línea ( I I ~ I , , ~ ~ ~ ) ) . Comportamiento de la topología propuesta con cb (]OFF) en el límite inferior. Graficas a potencia nominal (1 OOW) de: (a) Vl.lnea(t), (b) ILinea(t).

Graficas a potencia nominal (100W) de: (a) Vi,(t), (b) V,(t). Cambio de carga de 40W a 80W, se muestran las variables: corriente en la carga Io(t), corriente de línea ILfnea(t), tensión de salida Vo(t) . Gráfica de T ~ T vs Po, Po varia de 20W a 1OOW. Diagrama de flujo de energía de la topología propuesta. Diagrama de flujo de energía del Reductor de Armónicos. Diagrama de flujo de energía de los convertidores que procesan mas del 150% de la energía. Diagrama de flujo de energía del convertidor que procesan el 100% de la energía. Diagrama de flujo de energía de los convertidores que procesan menos del 100% de la energía. Lista de componentes. Coinparación de la topología propuesta con otras topologías presentadas por diversos autores.

43 44 45 49 50 50 51 52 52

53

55 56 57 51

5R

58

59 59 60

60 61 61 62

62

62

55 63

F-3

En la actualidad se ha incrementado en gran medida la proliferación de equipos electrónicos, debido en gran parte al desarrollo constante de la tecnología, así como el progreso continuo en las técnicas de manufactura y el diseño de componentes electrónicos. Estos equipos requieren de una fuente de alimentación de altas prestaciones considerando la problemática asociada al uso eficiente de la energía eléctrica.

La característica no lineal que está presente en todas las fuentes de alimentación, que basan su entrada en una etapa de rectificación y filtrado, provocan una bajo factor de potencia (FP) y una alta distorsión armónica total (THD). El efecto es que se contamina la red eléctrica, lo cual puede provocar fallas o descomposturas de otros equipos.

Desde hace aproximadamente 15 años, se inicio la preocupación por resolver este problema de uso inadecuado de la energía, desarrollando convertidores que corrigen el FP y que tradicionalmente se conectan en cascada con la típica etapa de conversión de corriente directa a corriente directa (cd-cd); esta solución tiene una baja eficiencia (11) y alto costo, por el exceso de componentes conectados en cascada. Sin embargo la respuesta dinámica (RD) es adecuada ya que se cuenta con etapas separadas para la corrección del FP y la regulación.

A partir de una rcvisión tlctallada dcl cstado del artc, en esta tesis sc propone una nucva topología dc Cuciitc aliiiiciilacióii qu i liciic una alla 11 (dcbitlo a un i i cstreicgia novedosa de manejo de la energía), asimismo corrige el FP, siendo este casi unitario, esto se logra sin descuidar la respuesta dinámica. Esto representa un avance significativo en lo que respecta a la investigación sobre fuentes de alimentación, debido a que hasta ahora, dos de los tres parámetros están en oposición. Cuando se mejora la 11 se descuida el FP, asimismo cuando se corrige el FP se descuida la q, sin embargo es posible mejorar estos dos parametros al mismo tiempo aprovechando el concepto de procesar menos del 100% la energía.

El documento de tesis esta organizado en cuatro capítulos. El primer capítulo (estado del arte), examina las propuestas de diversos autores publicados en los congresos más importantes de la Electrónica de Potencia (PESC: Power Electronics Specialist Conference y APEC: Applied Power Electronics Conference), y finaliza con el planteamiento de la topología propuesta para este trabajo de investigación.

El capítulo dos (teoría de operación y análisis teórico de la solución propuesta), muestra las ecuaciones de diseño y formas de onda del convertidor propuesto que ayudan a entender su funcionamiento, al final se muestra un ejemplo de diseño.

El capítulo tres (Estrategia de control), muestra el análisis y diseño de la etapa de control del convertidor propuesto por modos deslizantes. Además se presenta la forma en que se implemeiitó iisicaniente dicho control.

1-1

El capítulo cuatro (Análisis de resultados), se divide en dos partes: sin~ulaciones y resultados experimentales. Adicionalmente se presenta un análisis comparativo entre el convertidor propuesto y los demás convertidores propuestos en el estado del arte.

Finalmente se presentan las conclusiones del trabajo de investigación en donde se plantean los puntos más importantes. A grandes rasgos se hace referencia a que los resultados obtenidos en el convertidor propuestos son muy satisfactorios pues se logra romper un compromiso entre la eficiencia y la corrección de factor de potencia, asimismo se logra tener una buena respuesta dinámica. Sin embargo existe la limitante de que la tensión de salida no puede ser inferior al valor máximo de la tensión presente en la línea de ca. Aun así existen aplicaciones viables del convertidor propuesto como en tarjetas de sistemas de telecomunicaciones y por si solo el convertidor representa una idea novedosa que puede explotarse para trabajos futuros.

1-2

Capítulo 1 ESTADO DEL ARTE

1.1. Introducción

Actualmente existe una problemática de uso inadecuado e ineficiente de la energía eléctrica en los sistemas de alimentación, el cual se va complicando aun más con el paso del tiempo, debido a la proliferación de equipos electrónicos que no incorporan alguna solución para dicha problemática. Esto ha ocasionado una tendencia hacía el desarrollo de sistemas que procesen con mayor eficiencia (q) la energía eléctrica. Además para hacer un buen uso de la energía, se les diseña para que puedan corregir el factor de potencia (FP) y por lo tanto eliminan la contaminación de armónicos en la red, los cuales provocan fallas o destrucción en otros equipos electrónicos. Adicionalmente se les puede diseñar para obtener una buena respuesta dinámica, lo cual asegura que se podrán contrarrestar eficientemente cambios de carga.

El presente capítulo trata sobre los convertidores ca-cd conmutados que han propuesto diversos autores. Estos han tratado de crear una topología que integre las siguientes características deseables en sus convertidores: alta eficiencia, corrección del factor de potencia y buena respuesta dinámica.

1

Se han reportado buenos resultados en los 'convertidores ca-cd, pero normalmente alguna dc cslus variables ticiicn tin valor pobrc. l i n gciicral cuando SI ticnc u11 bucn 1l' y una buena respuesta dinámica se tiene una q baja (convertidores ca-cd con dos etapas) [l- 51. Cuando se tiene una alta q y una buena respuesta dinámica se tiene un FP pobre (convertidores ca-cd con una etapa de procesamiento y los que no procesan toda la energía) [6- 1 O ] .

En esta tesis se propone una topología donde se espera obtener una alta q (95-96%), un FP casi unitario y una buena respuesta dinámica. Para esto se utilizará el concepto de utilizar dos fuentes en serie con la finalidad de obtener una alta q, para corregir el FP y tener una buena respuesta dinámica. Se utilizarán dos etapas en una configuración diferente a la convencional y un controlador robusto.

1.2. Panorama general

- - +

- -

Actualmente el ahorro de la energía eléctrica se ha vuelto una de las metas más importantes en todos los niveles, debido en gran parte a que. su demanda crece año con año en forma indiscriminada.

- - - Pie-regulador Regulador

'1 C1 '1 C?

-

La conversión ca-cd no ha sido la excepción, por lo que se busca que se empleen métodos de diseño que permitan aprovechar al máximo la energía eléctrica para poder obtener una q alta, sin descuidar que se haga un buen uso de la energía, es decir realizando la corrección del FP. Es importante recordar que otro parámetro importante en dichos convertidores es la respuesta dinámica, por lo que no debe descuidarse.

El esquema tradicional que intenta mejorar estos tres parámetros se muestra en la figura 1.1, se basa en conectar en cascada dos convertidores. El pre-rcgulador tieiic como función principal la de corregir el FP. El otro convertidor tiene como función principal la de regular la tensión de salida (Vo(t)). La eficiencia total ( q ~ ) del convertidor es el producto de las eficiencias individuales ( ~ C I y qc2) de los convertidores, el resultado es que q~ no es tan buena; por lo que este es el principal inconveniente de esta topología.

L

ESTADO DEL ARTE

1.3. Esquemas propuestos en la literatura

Además del esquema tradicional de dos etapas, existen otros que tienen menos etapas y/o procesan menos la energía, sin embargo siempre hay un compromiso entre la q, el FP y la respuesta dinámica, esto trae como resultado que alguno de estos parámetros no tenga un valor óptimo. Las topologías propuestas se pueden clasificar de la siguiente manera:

Convertidores ca-cd iradicioiial con dos eiapas. Coiivertidores c a d con una etapa de procesamiento de la energía Convertidores ca-cd que procesan menos del 100% de la energía.

1.3.1. Convertidores ca-cd tradicional con dos etapas

Este tipo de convertidor es una mejora a la topología típica basada en dos convertidores cd-cd en cascada, dicha mejora consiste en que el regulador es significativamente más eficiente debido a que una parte de la energía se transfiere directamente a la carga. Actualmente existen tres esquemas que entran dentro de esta categoría [l-51. . '

El primero [ I ] se basa en un regulador con dos .entradas según se muestra en el diagrama de bloques de la figura 1.2 y el diagrama esquemático se muestra en la figura 1.3. El pre-regulador es un convertidor Flyback con dos salidas. El regulador es un convertidor Reductor con dos entradas, denominado en ese artículo como convertidor TIBuck (Two- Input Buck).

-

-

%=qclqc2

Diagrama de bloques de un converiidor ca-cd con un regulador muy cricieiiie, de la relerelicia 111.

Figura 1.2

Pre-regulador Regulador

Figura 1.3 Diagrama esquemático de un converiidor ca-cd con un regulador muy eficiente, de la referencia [I].

3

ESTADO DEL ARTE

V,(t) R v,(I) V J ~ l - V d ~ l

VAt) VStI

(4

El punto principal de esta topología es el convertidor TIBuck. En la figura 1.4 se muestran varias conversiones originadas del circuito principal, el cual se muestra en la figura 1.4(a). En esta figura se observan las tensiones Vi(t) y Vz(t), provenientes del convertidor Flyback, las cuales son convertidas a las tensiones Vi(t)-V,(t) y V2(t) en la figura 1.4(b). La resistencia de carga (R) fue dividida en dos partes (RI y R2) de tal forma que se tuvieran dos tensiones de salida (V,(t)-V,(t) y V2(t)).

== R1 V m W 2 ( t )

R, VJt)

(d Figura 1.4 Modificaciones del convertidor TlBuck para estimar su eficiencia total (uzR), (a) estructura

básica, (b) modificaciones en las fuentes de alimentación y en R, (c) estructura final.

Debido a lo anterior una parte de la energía disponible a la entrada se trasmite a la carga con una eficiencia VR, y el resto se transfiere directamente a la carga. El resultado final es que la eficiencia global del converíidor TIBuck ( 1 1 2 ~ = 97%) es sigiiificativaiiieiite mayor a la de un coiivertidor Reductor convencional. Esto trae como consecueiicia que la elicieiicia total (q.I), aproxiniadaiiiciitc 88%, de la topología propuesta sea mayor a la q ' r de la típica topología basada en dos convertidores en cascada, pero aun siguc siendo relativamente baja, debido a que el pre-regulador no procesa toda la energía. La rcspticsia dinámica es muy buena y el FP es casi unitario.

En [2] se presenta una versión mejorada de la topología anterior, la cual ya no presenta las siguientes desventajas:

El pre-regulador debe tener dos salidas y por lo tanto se necesitan mas elementos que en un pre-regulador con solo una.

A

ESTADO DEL ARTE

. EI capacitor de salida del convertidor TlBuck siempre esta cargado aunque este apagado el interruptor de este convertidor, por 10 tanto no se Puede implementar una protección contra corto circuito en el regulador.

En estas condiciones, en esta topología (figura 1.5) se tiene la ventaja que ei regulador tiene una sola entrada y por lo tanto el pre-regulador (convertidor Flyback, convertidor Elevador, etc.) solo debe tener una salida. Dicho regulador tiene una forma de conectarse tal que permite que V,(t) sea la suma de la tensión de entrada (Vop(t)) mas la tensión de salida del convertidor (Vco(t)). Entonces parte de la energía es entregada directamente a la carga (R) y otro tanto por el convertidor. El resultado es el mismo que en el caso anterior, es decir una fraccion considerable de la potencia de entrada (típicamente el 85-90%) se entrega a R sin pasar por-una etapa de procesamiento y por lo tanto con una q aproximadamente unitaria. El resto de la energía es entregada a R a través de un coiiVci.l¡clui. c d - ~ d (coiivcrLiJoi. Ilyback) cuii uiiü cicrh cliciciiciu (iic2). 1111 cuIiscG~icII~iii ~1 rcgtilador tiene una alia 11 (típicaiiiciite dcl 97'Xi). Además la i1,, es iiitiy cercaiia a la eficiencia del pre-regulador (Ilci), pero siempre mas baja, alrededor del 88%. Uii circuito completo de este esquema se muestra en la figura 1.6.

Figura I 5 Diagraina de bloques de un convertidor ca-cd con un regulador niuy eficiente, de la referencia [2].

Pre-regulador

rl C I

Regulador

Figura I .G .Diagraina esquein8lico de iiii coiivcrtidor ca-cd coil ti11 regulzidor' ii l i iy, elicicilte. de la rcfcrciicin [2].

En [3-51 se propone una familia de convertidores ca-cd, cuyo diagrama de bloques se muestra en la figura 1.7. El pre-regulador corrige el FP y el regulador mantiene regulada la tensión (V,(t)) en la carga (R) con una alta eficiencia (qcz), debido a la forma en que esta conectado (el regulador y R están en serie).

5

ESIADO DEL ARTE

~i~~~~ 1.7 Diagrama de bloques'de las topologlas presentadas en las referencias í3-51.

~1 pre-regulador se conecta después del puente rectificador y en su salida se encuentran dos capacitores (cb y C,), El capacitor C, se.encuentra en paralelo con R. El capaciíor voluminoso (Cb) se utiliza para almacenar energía y mantiene una tensión con un rizo de baja frecuencia. El regulador toma energía de cb y la libera a R.

La carga I< es aiiinciitada por aiiibos iiiúdulos (pre-rcgulador y cl rcgtilador). El PIC-

regulador entrega a la carga una corriente lop(t) y el regulador entrega una corriente I,,(t). La suma de ambas corrientes en R es igual a una corriente constante (Io(t)) y por lo tanto también .V,(t) es constante. La corriente Iop(t) fluye a través del arreglo .en serie de CdIR y Cb. La multiplicación de dicha corriente por la tensión en C, y cb es igual a la potencia de salida (Po).

1.a potencia dc salida dcl pre-regulador (P<,,,) se divide c i i dos coiiipoiiciites (Pi,¡, y R,,J debido a la configuración de la topología, sus. valores queclan determinados iior C,, y cb . La principal ventaja dci regulador cs qiic P,,ir sc libcra dircctaiiiciilc a R y por lo laiilo la eficiencia global (111.) se ve beneficiada. El regulador provee a.R el resto de la potencia (Por). Entonces Po es igual a la suma de Poi, mas Por,

El pre-regulador es un convertidor Flyback, figura 1.8, y el regulador es un convertidor Reductor-Elevador. Se observa en dicha figura que el capacitor de salida del convertidor Flyback se dividió en C, y cb. Además la entrada del convertidor Reductor- Elevador está en serie con R.

AI igual que en los casos anteriores la qr = 88% no es muy buena debido a que el pre-regulador procesa toda la energía.

Figura I 8 Diagrama esquenibtico de las topología presentada en la referencia [3]

6

1.3.2. Convertidores ca-cd con una etapa de procesamiento de la energía

Estos convertidores procesan el 100% de la energía [6-91, por lo tanto tienen una relativamente alta (90%). La respuesta dinámica es buena debido a que se utiliza un capacitor de almacenamiento a la entrada, pero por lo mismo el FP es pobre. Entonces existe un compromiso entre el FP y la q. Básicamente este tipo de convertidores se dividen en:

Convertidor con dos entradas. Conformador de corriente de línea (AICS por sus siglas en inglés).

Converiidov con dos eniradas

En los artículos [6-71 se presenta un convertidor (ver la figura 1.9) con solo una etapa de conversión y con dos entradas. Este tiene una q relativamente alta (90%) debido a que procesa toda la energía, con una respuesta dinámica rápida que ocasiona un FP inferior a la unidad a tal grado que sólo en el límite se logra cumplir con la norma IEC-1000-3-2, sin embargo el circuito es muy sencillo.

R

1:igura I .9 Diagrama de bloques del coiivertidor presentado eii las relereiicias 16-71

Un ejemplo de un diagrama esquemático del convertidor de la figura 1.9 se muestra en la figura 1.10, el cual como se puede observar esta basado en el convertidor Flyback. En este esquema se adiciona una rama auxiliar a dicho convertidor, la cual comparte el mismo interruptor. Esta rama está compuesta por el transformador T2 y el diodo D2. Esta rama se alimenta por medio de un capacitor voluminoso (Cb), el cual se carga en los picos de la tensión rectificada de la línea de ca (V,"(t)) a través de Ds.

Figura I .IO Diagrama esquemático del convertidor presentado en la referencia [6] .

Los diodos D, y D4 son necesarios para eliminar la circulación de corriente entre las ramas dcl convertidor Flyback.

7

El objetivo de este convertidor es alimentar la carga (I¿) por medio de ambas entradas (Vl,,,(t) y V,-b(t) = tensión en el capacitor voluiniiioso Ch). La mayor parte de la energía que consume R es tomada de V,,,(t) y prácticamente cb proporciona energía en 10s cruces por cero de V,,(t).

Conformador de corriente de línea (AICSpor sus siglas en ingle's)

Este convertidor presentado en [8-91 mejora el FP haciendo conducir por más tiempo los diodos rectificadores, esto se logra retroalimentando la energía disponible en una salida auxiliar (V,z(t)) del regulador, hacía el capacitor voluminoso (Cb) (figura I . 1 l(a)). El valor del ángulo de conducción ($c) de la corriente demandada a la línea de ca (ILinea) con respecto a la tensión presente en la línea de ca (VLine,(t)), figura 1.1 I(b), depende la cantidad de la energía retroalimentada. Entre más energía se retroalimente, $c se aproxima más a 90' pero q decae, por lo tanto es necesario hacer un compromiso entre el F P y l a q .

_ _ -- , V I d ) D,

c, 7;

8

ESTADO DEI, ARTE

1.3.3. Convertidores c a d que procesa menos del 100% de la eiiergía

Antes de examinar este convertidor, se explicará el concepto de procesar una porcentaje de la energía total. Primero se observa en la figura 1.13(a), el diagrama de flujo de energía para un convertidor que procesa el 100% de la energía, esto implica que toda la energía disponible a la entrada debe pasar a través de la etapa. En la figura 1.13(b) se observan dos etapas en cascada, cada una de ellas procesa toda la energía, por lo tanto es factible decir que en conjunto los dos convertidores procesan el 200% de la energía.

En la figura 1.13(c) se observa como un convertidor procesa menos del 100% de la energía. Dicho de otra forma un porcentaje de la energía de entrada se libera directamente a la salida, y el porcentaje restante se hace pasar a través de un convertidor y después el convertidor idealmente entrega la energía restante a la carga.

Procesa toda la energla Procesa 200% de la energla

desallda :

14 lb) Procesa menas del 100% de la energia

IC) Figura 1.13 Diagrama dc Ilii,jo dc iiiaiic,jo de eiici-gla eii (in coiivcrl idor ca-cd. (a) proccsa e l 100%~ dc la

energla, (b) procesa e l 200% de la energla, (c) procesa iiieiios del 100% de la eiiergia.

Parte de la energía procesada por un convertidor se desperdicia en forma de calor; por lo que ocurre que entre más energía maneje el convertidor son mayores las pérdidas, por lo tanto es lógico pensar que se debe minimizar la cantidad de energía que procesa dicho convertidor,

En la figura 1.14(a) se muestra el'diagrama de bloques del convertidor que no procesa toda la energía, presentado en [ IO] y en la figura I . 14(b) un. diagrama simplificado. Debido a que V,(t) = Vi,(t) + V,,(t), la potencia (Po) consumida en la carga'(R) también es la suma de las potencias entregadas por la red y el regulador, Pi, y Po, respectivamente, por lo tanto el convertidor no procesa toda la energía disponible en la entrada y como resultado se obtiene una t l ~ alta, además debido a ,que la etapa de control esta desarrollada por'una técnica de control robusto (control por modos deslizantes: SMC por sus siglas en inglés) se obtiene una buena respuesta dinámica, pero debido a que se utiliza un capacitor de almacenamiento a la entrada, figura i.l4(c), para proporcionar energía en los cruces por cero, el FP es muy pobre.

9

ESTADO DEL ARTE

íb)

Convertidor principal

( C )

1;igui-a 1.14 Coiiveriidor ca-cd que procesa iiieiios del .100%, de la ciicrgla, (a) diagrmia dc bloqtics, (b) circuito simplificado, (c) diagrama de bloques con capacitor de almacenamiento.

1.4. Solución propuesta

1.4.1. Planteamiento general

Actualmente se ha logrado hacer que un convertidor ca-cd tenga una buena eficiencia con una buena respuesta dinámica, pero con un factor de potencia bajo. Asimismo se han desarrollado convertidores ca-cd con un excelente factor de potencia y buena respuesta dinámica pero con una baja eficiencia.

Para obtener una eficiencia alta, corrección del factor de potencia y una buena respuesta dinámica se propone una nueva topología de convertidor ca-cd, figura 1.15, que debido a que no procesa toda la energía se obtiene una eficiencia alta, además el factor de potencia y la respuesta dinámica son optimas porque la topología integra dos convertidores cd-cd (pre-regulador y regulador). El pre-regulador se preocupa principalmente por corregir el factor de potencia y el regulador por mantener la tensión de salida (V,(t)) constate con una buena respuesta dinámica.

1 .O

ESTADO DEI, ARTE

1.4.2. Etapa de potencia

El convertidor propuesto tiene el mismo número de etapas que un convertidor convencional de dos etapas en cascada, y por lo tanto aproximadamente los mismos elementos (figura 1.16). Sin embargo debido a que procesan menos del 100% de la energía, estos elementos manejan menos potencia y por lo tanto pueden ser más pequeños y menos costosos. Asimismo la eficiencia global ( q ~ ) es más alta que la ql de la solución típica de dos convertidores en cascada..

Regulador

Figura 1 .I6 Diagrama esquemático del convertidor'propuesto.

El pre-regulador se eligió basándonos en que su función principal es corregir el FP. Este es un convertidor cd-cd Elevador bidireccional en corriente denominado como Reductor de Armónicos en [I I] . Para corregir el FP el pre-regulador se comporta como un filtro activo pero en cd (ver la figura 1.15), es decir demanda una corriente (ILH) de tal forma que sumada a la corriente (Io) que demanda ia carga (R) el resultado sea una corriente senoidal rectificada (I,,,), y por lo tanto la corriente demandada a la línea de ca ( I L ~ " ~ ~ ) sea senoidal y en fase con la tensión presente en la línea de ca (VLlnea).

11

ESTADO DEL ARTE

El regulador es un convertidor Flyback, este permite mantener constante y bien regulada la teiisiciii V,,, 'aún cuando la tensión Vi,, varía hriiscalnelite. para ello se ~i t i l i za un coiitrolador basado en la estrategia de SMC. Esta cslralcgia dc coiilrol Iaciiita cii gi'>Ui

iiicdida que cI regulador piicda ciitrcgar una fnriiia de onda Vc,, que conipleineiiie a Vi,, lo cual permita tener una V, constaníe, en 'el capítulo dos se analizarán a detalle el comportamiento de ambos convertidores. 1.4.3. Objetivos

El objetivo general del proyecto de investigación es:

Diseñar e implementar un convertidor ca-cd que no procese toda la energía con la finalidad de obtener una alta q, un FP aproximadamente unitario y una buena respuesta diiiániica.

Los objetivos particulares son:

Construir un prototipo experimental de baja potencia (100W) de la topología propuesta. Realizar simulaciones que describan el funcionamiento de la topología. Diseñar un control basado en el método de modos deslizantes. Hacer un estudio detallado al prototipo a desarrollar y compararlo con otras topologías presentadas por diversos autores.

12

Capítulo 2 TEORÍA DE OPERACIÓN Y ANÁLISIS TEÓRICO

DE LA SOLUCIÓN PROPUESTA

2.1. Introducción

Se presenta en este capítulo el análisis niateniático del convertidor propuesto. Se aplica el concepto de utilizar dos fuentes en serie, lo cual permite que el convertidor propuesto no procese toda la energía, y se'establecen ecuaciones de diseño. Se.analizan los convertidores involucrados en la topología, el pre-regulador (convertidor Elevador bidireccionai en corriente) y el regulador (Flyback). Por último se muestra el diseño del convertidor, el cual es necesario para la construcción del prototipo.

2.2. Obtención del diagrama esquemático

El 'convertidor propuesto, como ya se mencionó, procesa menos del 100% de la energía, y por lo tanto sus ekmentos'que-lo integran manejan menos energía y pueden ser más pequeños en comparación con un convertidor que procesa toda la energía o el convertidor tradicional con dos etapas en cascada:

13

TEORiA DE OPERACIÓN Y ANALISIS TEÓRICO

PI"

Para poder construir el converiidor es necesario partir de la figura 2.1, la cual muestra un diagrama de flujo del convertidor, esta es la forma más simple de mostrar la idea principal de la propuesta. En esie diagrama se observa, quc una parte de la energía (PO,,) se libera directamente a la carga y el resto (P,,,,) pasa a través de una etapa de conversión, que teóricamenie puede ser cualquier converiidor, éstc a su vez entrega el resto de la energía (PcO) a la carga con cierta eficiencia ( q ~ ) .

Po = PDI, + pc.

PI" Po = PDI. + pc.

PDI, = PI" - PI",

PI", ' IC? '1 c2

14

3

TEORiA DE OPERACIÓN Y ANÁLISIS TEORlCO

cd-cd

Figura 2.3 Transformaciones de la topología propuesta (a) Diagrama eléctrico simplificado del convertidor propuesto, (b) diagrama eléctrico con las sustituciones de las fuentes ideales VI y V2 por las fuentes V,.(t) y V,.(t) respectivamente.

Regiadw

íbl

Figura 2.4 Diagramas de bloques y .esquemático de la topología propuesta, (a) bloques, (b) esquemático.

El pre-regulador se utiliza para corregir el FP y el regulador para mantener regulada V,(t) con una buena respuesta dinámica. Se observa entonces que en esta topologia propuesta se aprovechan los beneficios de aplicar los conceptos de no procesar toda la energía para mejorar la eficiencia, y el de usar dos etapas con una nueva forma de conectarse para corregir el IT y tener una buena respuesta dinámica.

La fracción (k) de la energía que es procesada por los convertidores cd-cd es, ver las figuras 2.2 y 2.3, es:

k = fracción de la energía total procesada por io convertidores. Pc0 = potencia de salida del regulador.

1s

T E O F ~ A DE OPERACIÓN Y ANALISIS TEÓRICO

p, = potencia de salida. pOlr = potencia liberada directamente a la carga. V,,(t) = tensión de entrada en función del tiempo. I,(t) = corriente de salida en función del tiempo. T =periodo.

Como Io(() es constante:

donde: l T v. = '. ' pi,, (t)dt

"' T o

VI, = valor promedio de V,,(t). I, = valor promedio de Io@).

Asimismo:

l T

TO Po = - jVo(t)Io(t)dt

como I&) y V,(t) son constantes:

donde Po = I,V,

V, = valor promedio de V,(t).

Despejando de (2.2) Pc, y sustituyendo en (2.1) se obtiene:

(2.5)

Sustituyendo (2.3) y (2.4) en (2.5) se obtiene: ..

Observando la ecuación (2.6) se deduce que la cantidad de energía k que procesan los convertidores cd-cd de la figura 2.4(a), está en función de la cantidad de Vi, proporcionada a la carga. Como ya se mencionó entre menos energía procesen los convertidores, k deberá ser lo mas pequeño posible y la eficiencia total (VT) de la topología propuesta es mayor. Entonces es necesario procurar que el valor promedio de Vi,,(t) sea lo mas cercano a V,.

Para encontrar'una expresión de la q ~ , es necesario basarnos en las figuras 2.5(a) y (b) definidas a partir de [lo]. En estas figuras se muestra que el pre-regulador puede entregar energía (Px) a la carga debido a que es bidireccional en corriente, por io que:

16

TEOdA DE OPERACIÓN Y ANALISIS TEÓRICO

donde: p,,, = p, +p, Pc, = kP,

P, = potencia entregada por el pre-regulador a la carga. P, = potencia entregada directamente a la carga por la red eléctrica. P,,,, = potencia de entrada del pre-regulador. P,,, = potencia de entrada de la topología propuesta. Pop = potencia de salida del pre-regulador. qcl = eficiencia del pre-regulador. qc2 = eficiencia del regulador. q~ = eficiencia total de la topología propuesta.

Sustituyendo (2.9), (2.10), (2.1 1) y (2.12) en (2.13) se obtiene:

Sustituyendo (2.14) en (2.8) se obtiene:

Sustituyendo (2.9), (2.12) y (2.1 5) en (2.7) se obtiene:

Po ‘Ir = -

Pi” Despejando Pi, de ecuación (2.16) y sustituyendo en (2.17) se obtiene:

(2. I 1)

(2.12)

(2.13)

(2.14)

(2.15)

(2.16)

(2.17)

(2.18) %‘IC2 1]T =

-(‘IC2 p, -‘Ic1’Ic2)+kO -‘Ic1‘Ic2)+ ‘1ciqc2 p.

17

TEOR~A DE OPERACI~N Y ANALISIS TEÓRICO

ib) U U

is1

Figura 2.5 Uiagranias de bloques y de flujo de la iopoiogia propuesia donde se considera el eíecío de la energía eniregada por el pre-regulador a la carga, ( a ) dc bloques, (b) de flujo .

Aunque no parece evidente en la ecuación (2.18) se puede tener una qr superior a la de un solo convertidor que procesa toda la energía para ciertos valores de k. Para evidenciar este hecho se presenta en la figura 2.6(a) una gráfica de la q~ contra k, en donde se supone que qci = qc2 = 0.9, Pi, = lOOW, P, = 1 W, como puede observarse en dicha gráfica para valores de k < 0.46 la q r el convertidor propuesto es superior a la eficiencia individual de un solo convertidor (qci 6 qc2). Asimismo en la figura 2.6(b) se puede observar el efecto de P, en la TT, para esto se supone que qci = qc2 = 0.9, Pi, = IOOW y que k = 0.4. Cuando P, se incrementa la I]T disminuye debido a que es una energía que tiene que procesar el pre- regulador.

o 94

O 92

o 9

o 6 3

083

O84

O 8 2 , \

o 0 2 0 4 06 O8 i k

Figura 2.6 (a) Gráfica de 'IT vs k, (b) gráfica de 'IT vs P,

La ciapa recíificadora se dcsprccio eii el análisis aiiierior, dcbido a que la cliciciicia (qu) de dicha etapa es casi unitaria. Para demostrar esto debemos basamos en la figura 2.7, en esta se muestra un puente rectificador con una carga resistiva, este análisis es válido para el convertidor debido a que es un emulador de resistencia.

(a) ib) Figura 2.7 (a) Puente de diodos, (b) Circuito equivalente para un semiciclo

18

TEOR~A DE O P E R A C I ~ N Y ANALISIS T E ~ R I C O

La eficiencia del puente rectificador es: 'ad

'ind r l V =-

donde:

Pi,,,, = Potencia de entrada de la etapa rectificadora. Pod = Potencia de salida de la etapa rectificadora.

'Se obscrva en la figura anterior quc: 1 1

(2.19)

(2.20)

(2.21)

donde: Vin,,,hx = valor máximo de Vi,(t). I,n,máx = valor máximo de Iin(t). Vo = caída de tensión en los diodos rectificadores (0.7V).

Por lo tanto sustituyendo las ecuacioiies (2.20) y (2.21) en la ecuación (2.19) y considerando que Vinmáx = 170V, T = 16.66ms, VO = 0.7V se obtiene:

l T 1 '

To - jYnrnaxsen ( w t ) I , " , " , P (wt)dt - - pvDI,"ma Isen (wt)Jdt

- IV,,,,,,sen(wt) I,,,,,sen (wt)dt

To (2.22) l T

T "

r l D =

qv = 0.99

2.3. Ecuaciones y formas de ondas esperadas

2.3.1. Pre-regulador (convertidor. cd-cd Elevador bidireccioiial en corriente)

El pre-regulador es un convertidor conocido como Reductor de Armónicos (HR por sus siglas en inglés) en [ l 1 J, (figura 2.8), es un convertidor Elevador bidireccional en corriente, es decir la corriente ILH(t) puede ser negativa ó positiva. Esto es posible debido a los diodos antiparalelos (DI y D2) de los interruptor M I y M2, por lo tanto este convertidor trabaja siempre en modo de conducción continua (MCC).

19

TEOR~A DE O P E R A C I ~ N Y ANALISIS TEORICO

Pre-eauladoi

I I I I 1

Diagrama esquemático del pre-regulador. Figura 2.8

En la figura 2.9 se pueden observar el comportamiento de algunas tensiones y corrientes importantes del convertidor propuesto durante un ciclo completo (Tc) de conmutación. Los interruptores MI y Mz funcionan en forma complementaria, por lo que se requiere de un tiempo muerto (Atin).

(a) íb) Figura 2.9 (a ) Forinas de onda del pre-regulador cuando 1~1.,(t) es positiva, (b) formas de onda del pre-

regulador cuando ILH(t) es negativa.

Análisis cuando I,,& es positiva, .figura 2.9(u): En el tiempo O<t<t,,, conduce el interruptor (MI), increinentándose la corriente I~ i i ( i ) , su diodo antiparalelo DI permanece bloqueado debido a que está polarizado inversamente. Después en el período t,,<t<Tc el que conduce es el diodo D2 y M2 permanece bloqueado debido a que la tensión presente entre sus terminales drenaje y fuente es negativa. Ei capacitor cb se carga durante ei tiempo de encendido O<t<t,, (por lo que la tensión VCb(t) se incrementa) y se descarga hacia la carga en el tiempo de apagado.(por lo que la tensión vCb(t) disminuye).

20

TEOR~A DE O P E R A C I ~ N Y ANALISIS TEÓRICO

Análisis cuando 1/,,./(1) es negativa, ,figura 2.90): En el período O<t<toll conduce el diodo D I y la corriente del l~ii(t) ,se incrementa, el interruptor M I no conduce pues su tensión drenaje a fuente es negativa. Después en el periodo t,,<t<Tc el que conduce es el interruptor M2 y la corriente ii.ll(t) decrece, el diodo D2 no conduce pues está polarizado inversamente. El capacitor Cb se descarga hacia la carga durante el período O<l<t,,, y en el tiempo de apagado también se descarga hacia la carga y hacia la red, por lo tanto la tensión VCb(t) siempre disminuye. Por io que es necesario que cb sea IO suíicientemente grande para qiic la tciisióii prescntc ciitre sus tcriiiiiialcs no disminuya por debajo de V,,,(i) durante la etapa eii que 1LII(t) debe ser negativa, pues esto ocasionaría que dicho capacitor tienda a cargarse y por lo tanto Ii.j,(t) se volvería positiva.

En base a la figura 2.9 y aplicando la ecuación que describe el comportamiento de los inductores a Lli se obtiene:

AIL,

At v,, = L, ~

Para el tiempo de encendido At = to, y tomando en cuenta que el rizo máximo de corriente (AILH,,,,~~) que se permitirá se da cuando VLH(t) = Vil,,,&x, se obtiene:

(2.23)

Para el cálculo del capacitor es necesario considerar el tiempo de almacenamiento (&) [13], para el limite superior (debido a que el límite inferior depende de que se satisfaga la condición V,(t) > V,,,,). El tiempo de almacenamiento AtA se define como el tiempo en el cual la carga va a seguir operando normalmente después de que se desconecta el convertidor de la red eléctrica, es decir cuando V,,(t) = O. Los valores de AtA típicos son entre 15ms a 50ms, en nuestro caso se escoge 50ms. Una consecuencia de escoger este valor relativamente alto es que la tensión VCb(t) nunca será menor a VI,,,,,& durante la operación normal del convertidor. La tensión Vop,,,ln es el mínimo valor al cual puede operar la carga, según la referencia un valor adecuado es de O.75Vn. Siii embargo este cálculo debe adecuarse a las necesidades de la carga, entonces:

(2.24)

La fiincjón de ganancia en tensión del convertidor Elevador es 1121:

-- VOP (4 1

v,,, (t) ' - D --

donde:

(2.25)

D = ton _ _ t o , - to , , + t o , T

Vo,(t) = tensión de salida del pre-regulador en función del tiempo. D =ciclo de trabajo. to,, = tiempo de encendido.

21

TEOIÚA DE OPERACI~N Y ANALISIS TEORICO

= tiempo de pagado

La gráfica de la ecuación (2.25) es:

O 0 2 0 4 06 O8 1

Figura 2.10 Gráfica de V.,(t)N,.(t) contra D

La tensión requerida a la salida del HR (Vop(t)) es constante, pero la tensión de entrada es variable (V,,(t)= V,,,,&en(wi)J), figura 2.11. Por lo tanto para generar una tensión de salida constante con esa tensión de entrada, es necesario que el ciclo de trabajo sea variable (función del tiempo).

60

40

20

t Ob2 O k 4 O006 OM8 O01 0012 0014 0016

Figura 2. I I Gráfica de la ieiisióii de eiiirada del pre-regulador (Vi,,(i)).

El ciclo de trabajo para este Vi,,(t) es, considerando que V,,(t) es constante:

(2.26) D = Ap-.--.- v - Vi",mlr lsen(wt)l

vu, donde:

= valor máximo de la tensión de entrada. w = frecuencia natural.

22

TEORiA DE OPERACION Y ANALISIS TEÓMCO

El ciclo de trabajo máximo (DM& ocurre cuando V,,(t) es mínimo (V,,,,e = O): v"p - 0 = 1 (2.27)

DM&x =

Gralicando la ecuación (2.26) sc oblieiic la figura 2.12:

D

(2.28)

t

Figura 2.12 Grhfica del ciclo de trabajo (D) esperado en el pre-regulador

Basándose en el diagrama de bloques de la topología propuesta mostrado en la figura 2.13, la ecuación de la corriente requerida a la entrada del convertidor elevador (Il.14t)) es:

(2.29)

(2.30)

Po = Potencia consumida en la carga. = valor efectivo de la tensión rectificada de la línea de ca.

23

TEOR~A DE OPERACI~N Y ANÁLISIS T E ~ R I C O

r + v,,W P,,, +

~

-" I I , - , I

+ Pre-regulador + Po, V,,(t)

~

I

1. 17igiira 2. I3 Diagrama di bloqtics di la iopologla propiicsin.

Sustituyendo (2.30) en (2.29) se obtiene:

Graficando la ecuación (2.3 1) se obtiene:

JLJt)

ILHN = I,",,dXIsen(4 - 1, (2.31)

Figura 2.14 Corriente de entrada del pre-regulador

La corriente de salida del pre-regulador se calcula considerando el balance de potencia (figura 2. i 5 ) :

pi,,, = Po, donde:

(2.32)

(2.33)

24

TEORLA DE O P E R A C I ~ N Y ANALISIS TEÓRICO

como V,,(t) es constante:

Po, = V J O P

donde. I,, = valor promedio de iop(l)

susiiiuyeiido (2.33) y (2.34) en (2.32) y dcspcjaiido I , , , : 1 '

TO - p . 1 1 O)V," ( t b

I = OP

V O P

(2.34)

(2.35)

Las pérdidas (PLP) en el pre-regulador son, considerando las pérdidas por

(2.36) conmutación despreciables:

PLp = I L , m J i - H + IL,Vc,,sat

RLH = resistencia serie del inductor LH. V C E , ~ ~ ~ = tensión de saturación de los IGBT's.

donde:

Por lo tanto la eficiencia ( ~ c I ) del pre-regulador es:

(2.37)

(2.38)

La potencia P, es:

1 'I 1 '

O T ,* px = T jLi (t)V,,,fi)dt + - j I L i i (t)v., (tbt

Como ambas integrales del lado derecho de la ecuación anterior son iguales, entonces:

(2.39)

Los períodos de integración (0,tt) y (t2,T) corresponden a los tiempos en que IL,,(t) es negativa, el valor de ti (utilizando la condición ILH(t) = O) es:

25

TEOR~A DE O P E R A C I ~ N Y ANALISIS TEÓRICO

(2.40)

(2.41) El valor de t2 es:

t, = T - t ,

2.3.2. Regulador (convertidor cd-cd Flyback)

El regulador es un convertidor Flyback (figura 2.16). Su,-función Principal es mantener regulada la tensión en la carga V,(t) con una buena respuesta dinámica. Es necesario este convertidor por que contiene una salida flotada, si no fuera así se haría un corto circuito.

v,,(ti izyp-+ C-0. V,,(t)

V,,Iti

Figura 2.16 Diagrama esqiieinático del regulador.

En la figura 2.17 se muestra las formas de onda para un ciclo completo (Tc) de conmutación. En el tiempo O<t<t,, conduce el interruptor M3 y el diodo D3 permanece bloqueado debido a que está polarizado inversamente, incrementándose la corriente iLI:(t), en este caso la energía se alniaccna en foriiia de campo magnético, asiinisnio en csíe periodo el capacitor ch se descarga a través dc la carga, ocasioiiaiitlo que lii tciisih V,,, ,( í) disminuya. Después en el período t,,,<t<'f~. cl que conduce es el diodo 113, dcbido ii q ~ c sc colapsa el inductor del secundario ocasionado que se invierta la polaridad de su tensión, mientras M3 permanece apagado, y la energía anteriormente almacenada se libera hacía el capacitor (Cb) y la carga, esto ocasiona que la tensión V,,(t) se incremente.

v,

" " ' 1 ... * ? q i i...' -, . . . . . . .

O I

" k p , %

Vc.l'I ..! !m

)L

o t

Figura 2.17 Forinas de onda del regulador para un ciclo de conmutación compleio.

26

TEORiA DE OPERACIÓN Y ANÁLISIS TEÓRICO

En forma análoga al análisis empleado en el pre-regulador para encontrar el valor de

L = (2.42)

to,, 1 o (2.43) c,, =

L i i , se efectUa el análisis para encontrar Lr y C,,, el resultado es:

1. OP

A l,,,##?hY

A",,,m*"

Este convertidor va a operar en MCC, por lo tanto tiene las siguientes funciones de ganancias en tensión y corriente utilizando el concepto de ciclo de trabajo (D) [12]:

(2.44) D (t) - M ~

V,,(t) 1 - D

(2.45)

donde: M = relación de vueltas del transformador. IFelit(t) = corriente de entrada del regulador en función del tiempo.

Graficando la ecuación de (2.44) se obtiene la figura 2.18:

v,,(t)N,,(t)

f lR ; D 0.2 0.4 ni 06 ._ O ..

Figura 2.18 Gráfica de la ganancia en tensión delconvertidor Flyback.

Despejando D de (2.44):

(2.46)

Analizando la figura 2.19, definida a partir de la figura 2.13, se deriva la siguiente

(2.47)

ecuación:

-vi" (t)- v,, (t)+V, (t) = o

27

T E O R ~ A DE O P E R A C I ~ N Y ANÁLISIS TEÓRICO

Figiira 2.19 üiagi-aiiia de I>Ioqtics dcl i-cgiiladoi. eii serie coi1 V,,,(t) y la c w a

Substituyendo Vi,(t) = Vi,,,,;r,lsenwt y sabiendo que V,(t) es constante en la

(2.48)

Se observa en la ecuación (2.48) que V, debe ser mayor que la tensión de entrada máxima (Vin,,,h) por que de lo contrario Vc,(t).sería negativa, y el convertidor Flyback solo produce tensiones positivas. Esto en consecuencia, limita el cainpo de aplicaciones de nuestro convertidor a cargas que requieran tensiones por encima de Vin,,ix.

ecuación (2.47) y despejando Vc,(t):

v,, (t) = v, - Vin.,"sx Isendl

Graficando la ecuación (2.48) se obtiene la figura 2.20.

Figura 2.20 Tensión de salida del convertidor Flyback.

Sustituyendo la ecuación (2.48) en (2.46) se obiieiie:

V" - Vi,,,,.n. Ise~1w~I

vo - Vin,msx Isendl + MV,, D = __-~ . (2.49)

Tomando en cuenta que M = 1 se grafica la ecuación (2.49) obteniéndose la figura 2.21:

Figura 2.21 Ciclo de trabajo D del convertidor Flyback.

28

TEORiA DE OPERACIÓN Y ANÁLISIS TEÓRICO

Como puede observarse en la ecuación (2.49), D M ~ ~ ocurre cuando Vin(t)= O, por 10 tanto:

(2.50)

131 ciclo dc trab-jo iiiíiiim« ociirre cuando la ieiis6n Vi,!(t) = Vi,,.,,,ar y esln datlo por la

vo - Vi..,"ax (2.51)

siguienle ecuación:

DM," = v, - Vin,max + MV,,

Utilizando un procedimiento análogo al que se utilizó para obtener la ecuación

V C J O (2.52)

(2.35), se obtiene la ecuación (2.52):

'Fe,,, = __ V O P

Las pérdidas (PLR) en el regulador, considerando las pérdidas de conmutación

(2.53) despreciables, son:

'LR = ':en, (Ron + 'LF)

kn = resistencia de encendido del Mosfet. RLI: = resistencia serie del inductor LF.

Donde :

La eficiencia (qc2) del pre-regulador es:

'Co

Po* qc2 =-

l ~ o p

Sustituyendo la ecuación (2.53) en (2.54) se obtiene:

(2.54)

(2.55)

2.4. Aspectos de diseño de la etapa de potencia

2.4.1. Especificaciones del convertidor propuesto

Con el propósito de comprobar el funcionamiento del convertidor propuesto se construyó el prototipo experimental en donde se consideró que V, debe tener un valor mayor a Vin,msx, como ya se mencionó en el apartado 2.3.2. Además se tomaron las siguientes especificaciones:

29

TEORiA DE OPERACIÓN Y ANÁLISIS TEÓRICO

Tensión de salida (Vo). 200Vdc Tensión de entrada ( V L ~ ) . 12OVac Frecuencia de V L ~ ~ ~ ~ 60Hz Potencia de salida (Po). 1OOWatts. Frecuencia de conmutación máxima 200kHz

Según la ecuación (2.6) la cantidad de energía procesada por los convertidores es, tomando el valor promedio de Vi,, : .,

"ill k = l - -

108V k = 1--- = 0.46

200v

v,

k = 0.46

2.4.2. Pre-regulador

El ciclo de trabajo máximo según las ecuación (2.27) es:

El ciclo de trabajo mínimo según la ecuación (2.28) es: D M f i ~ = '

200v -120-/2v D,, = __

D,, =O.lSl 200v

Por lo tanto se espera que D varíe dentro de esos valores

Según la ecuación (2.23) el valor de LH es, tomando en cuenta que b,, = 9ps, A I L H , ~ ~ ~ = 0.3A y que Viii,n,~x = 170V:

170V(9ps) 0.3A

L,i =

L, = 5.lmH = 5mH

Según ia ecuación (2.24) ei valor de cb es, considerando que At,, = 501iis, P, = 1 oow, v,, = 200v y V",,",I" = 1 sov:

30

TEORiA DE OPERACION Y ANÁLISIS TEÓRlCo

Por lo ianto escogemos un cayaciior de 47OpF, el cual nos da u n A h = 4inls.

Según la ecuación (2.30) el valor de ILH(t) es: Po &

i,,(t)=-(senwt(-~, vim

r 1oowv2 lsen2n60tl- 0.5

120v ILH(t)=

ILH(t)= i.l81seii377t(- 0.5

La eficiencia del pre-regulador (qc1) según la ecuación (2.38) es, considerando que

V,, (t) = 120fi~siii377tl, RLI, =16.4R y la V C E , ~ ~ ~ de los IGBT's G20N60B3D es 2.2V:

En la figura 2.22 se muestra una gráfica de 9 ~ 1 cuando varia la resistencia R1.14, debido a que esta varia con respecto a la frecuencia de conmutación, cuando se increineiita la frecuencia se incrementa RLl.1 y viceversa. Entre nias grande sea el valor de 1<,-1, inayores son las perdidas.

C I

Figura 2.22 Gráfica de qci vs RLI+

3 1

De acuerdo con Ins ecuacioncs (2.40) y (2.41) y sabiendo que 1' = 8 33m. los valores de ti y t2 son:

t, = 1.16ms

t , = T - t ,

t, = 8.33ms - 1.16ms t, = 7.2ms

El valor de Px aplicando la ecuación (2.39) es: 2 'I

T o p, = - jIL.1, mi" ( t b

P, =1.66W

Como se observa esta cantidad representa el 1.66% de la potencia total consumida e11 I:i carga, csio sc ~ichc a quc lii corriciiic ll.ll(i) cs licyativa c c r ~ LIC los cruces por cero tlc Vi,,(t), por lo que es posible despreciar esta variable con la finalidad de obtciicr una ecuación más sencilla. por lo tanto la ecuación (2.18) se resume a:

2.4.3. Regulador

El ciclo de trabajo máximo según la ecuación (2.50) es:

vo V, +MV,,.

200v

%I$? =

DM$x = 200v + l(200V) DMAX = 0.5

El ciclo de trabajo mínimo según la ecuación (2.51) es:

v, - V , d X

V" - vlr,,t"ax + MV,, DM," =

200v - 12045v 200v - i20../2V + l(200V)

D.;,,, = ~ ~ _ _ _

DMl,, = 0.13

32

Por lo que se espera que D varié entre 0.13 y 0.5.

Según la ecuación (2.42) el valor de LF es, tomado en cuenta que A I L F , ~ ~ ~ = 0.2A cuando V,, = 200V y que to,, = 1 . 5 ~ s :

V O P t o ” L, =

AILF,max

L, = 800~1-I

De acuerdo con la ecuación (2.43) el valor de C, es, considerando que A V C , , ~ ~ ~ = OSV y que I, = OSA:

1 . 5 ~ s OSV

c, =- 0.5A = 1.5uF

Para poder generar adecuadamente la envolvente de tensión de la figura 2.20, es necesario tratar disminuir lo mas que se pueda el valor de C,. Sin embargo con un capacitor deniasiado pequefio se tendría un rizado inuy grande, por lo tanto tin valor comercial adccuatlo de C,, es dc 1.2pF.

IA cliciciicia (yL*) clcl rcgulaclor cs, scgúii la ccuaci6ii (2.55), donde l a I<,,,, dcl Mosfet IRF840 es 035Q y RLF = 7.1Q-2:

’ OP qc2 = 0.98

En la figura 2.23 se muestra una gráfica de qc2 cuando varia la resistencia RLF (debido a que su caso es similar al de la resistencia RI,H) es decir esta varia con respecto a la frecuencia de conmutación, asimismo cuando se incrementa la frecuencia se incrementa RLI: y viceversa. Por lo tanto ocurre que entre mas grande sea el valor de RLF mayores son las perdidas.

33

TEORIA DE O P E R A C I ~ N Y ANALISIS T E ~ R I C O

La eficiencia total (qT) según la ecuación (2.18) es: r l c i v c z

7 T = %lCZ -rlcivC2)+k0 - v c i r l c 2 ) + v c l r l c 2 1'"

0.91(0.98) r l - ' - E ( 0 . 9 8 -0.91 (0.98))+0.46(1-0.91(0.98)) + 0.91 (0.98)

IOOW v i = 0.945

En la figura 2.24 se muestra la gráfica de q~ cuando varia RLF y RLH:

Figura 2.24 Gráfica de qr vs RLF y RLH.

Se observa en el diseño del convertidor, que los capacitores e inductores tienen valores relativamente pequeños, io cual contribuye a generar adecuadamente las envolventes requeridas en las tensiones y corrientes del convertidor propuesto. A excepción del capacitor Cb, el cual es un elemento diseñado para almacenar energía con la finalidad de otorgarla a la carga en la región cercana a los cruces por cero y cuando la red se desconecta.

2.5. Aplicaciones del convertidor propuesto

Una aplicación viable de la topologia propuesta es en sistemas distribuidos, figura 2.25. Con esla topología sería posihlc aliineiilai. u n número considerable de cargas. conservando una alba cíiciciicin y con coinpoiicnies quc iiiaii<jcii mciios poicnci;i qiic cl convertidor tlpico dc dos ctapas cn cascatln y por lo iaiiio con la posibilidad de qtic scan más baratos. En este caso sería una solución intermedia entre los filtros activos que manejan altas potencias y los convertidores ca-cd que se integran en algunos equipos que manejan baja potencia.

34

TEOR~A DE OPERACI~N Y ANÁLISIS T E ~ R I C O

- V& + I I

+ Pre-regulador - Regulador VJt)

. 4 I

..

- Carga No. I

5 __

Carga No. 2

r -

Carga No. 2

vLlnea(t) \ 4 VI:) Pre-regulador Regulador VJt)

I

Lámpara

Inversor

Lampara

Ahora la eficiencia total (q,r2) es, en la cual se considera la eficiencia (qx) de las etapas conecíadas a la salida del convertidor propuesto:

35

TEORIA DE O P E R A C I ~ N Y ANÁLISIS TEÓRICO

Las ventajas de estas aplicaciones son:

El convertidor propuesto realiza la corrección del FP con una buena respuesta dinámica. Por lo tanto los convertidores que están como carga no tienen que esforzarse demasiado, esto iniplica que su etapa de control puede ser sencilla. El convertidor propuesto no maneja toda la potencia de entrada por lo que sus elementos pueden ser más pequeños.

Desventajas:

La eíicieiicia global (q.1.2) de la aplicación se ve aicctada debido a qne están en

balastros. Sin embargo este efecto se ve minimizado debido a la alta eficiencia del convertidor propuesto.

cascada cI convci.tidoi pro~"lcsto con las tal:jctas dc tclccoillliiiicncioilcs/

36

Capítulo 3 ESTRATEGIA DE CONTROL

3.1. IntroducciOn

En este capítulo se presenta el análisis de la etapa de control por modos deslizantes (SMC, por sus siglas en inglés) utilizada en el convertidor propuesto. Se desarrolla un modelo matemático del convertidor en variables de estado, se realiza el análisis de existencia del modo deslizante del sistema.

3.2. Estrategia de control

3.2.1. Condiciones de operación

La etapa de conirol tiene que “obligar” al convertidor propuesto a proporcionar formas de tensión y corriente con excursiones relativamente grandes, por ejemplo el pre- regulador, figura 3.1 (a), tiene que deiiiaiidar titi tipo de corriente (It,lI(i)) quc varia eiiire valores posiiivos y iiegaíivos con una liccueiicia de 120 llz, ligura 3 . I(b).

37

P,B.B!gY r-

I I I :." (b)

(a)

Figura 3 1 (a) Diagrama esquemático del pre-regulador, (b) Corriente demandada por el pre-regulador

La tensión de salida del regulador (VC(,(t)) está en serie con la tensión rectificada de la línea de ca (V,"(t)) y con la carga, figura 3.2(a). Por lo tanto el convertidor propuesto tiene que proporcionar una forma de onda que varía desde un valor relativamente cercano a OV al valor de tensión de salida (V,(t)) requerida en la carga, figura 3.2 (b), y también con una frecuencia de 120Hz. Entonces se necesita que la etapa de control sea io suficieiiteniente rápida para proveer ese tipo de excursiones y para cuando se presenten cambios de carga repentinos.

Vc0lt)

2401 ?>O

i"i Flyback

0@206C¡4 0 ' ~ O ' h ' 001 '0012 O014 06 t

(a) ib) Figura 3.2 (a) Diagrama de bloques del regulador, (b) tensión eniregada por el regulador

Las estrategias de control clásico (las cuales se aplican a sistemas lineales) se restringen a convertidores con pequeñas variaciones en las variables de estado, se sintonizan alrededor de un punto de operación, por lo tanto su desempeño en la topología propuesta no sería muy bueno. Por otro lado existen estrategias de control robustas que permiten seguir envolventes con variaciones considerables y además aseguran que el sistema a controlar tenga una respuesta dinámica (RD) rápida. El SMC es una técnica de control robusto, el cual ya se ha utilizado y obtenido resultados muy satisfactorios en sistemas similares al propuesto [lo].

38

El convertidor propuesto prcseiita una csiructuru variablc, dctcriiiiiiucla pcir 101:

dispositivos de conmutación y como se verá más adelante el modelo matemático es una ecuación en variables de estad.0 no lineal, por lo que la estrategia SMC es una buena opción, debido a que dicha estrategia está basada en la teoría de sistemas de estructura variable y se utiliza en sistemas no lineales.

3.2.2. El control por modos deslizantes (SMC)

El SMC permite que el sistenia retroalimetado presente características tales como robustez, buena RD, estabilidad ante variaciones grandes de carga y de Vin(t), entre otras. Una de sus desventajas es la complejidad de la teoría involucrada [14].

El SMC, a partir de la definicibii de una superficie denominada de deslizaniiento (cr) ‘‘atrae” al sistema hacia ella, hace que cl sisieiiia periiianezca alii, llevando al sistema a titi

punto de operación deseado una vez que sc llega a la superficie deliiiida. Para í‘acilitar la comprensión del funcionamiento se utilizará un ejemplo [ 151:

Sea el sistema:

x i =x* (3.1) x , = - a x , - b x , + u

Donde la ley de control u es de la forma:

Sc propoiic una siipcrficic dciioiiiiiioclo siipcrlicic dc tlcsliz;iiiiiciii«:

Para completar la ley de control:

11 = - ipX

< J = c x , +X) = o

a . x , o > O

v = -a x , o < o

(3.2)

(3.3)

(3.4)

(3.5)

El sistema definido presenta dos estructura de acuerdo con la ley de control, una asociada con a y la otra con -a. Supongamos que el valor de a es tal que los planos de fase para cada situación son los que se muestran en las figuras 3.3 y 3.4.

Figura 3.3 Plano de fase para a

3 0

ESTRATEGIA DE CONTROL

Figiira 3 4 Plaiio de fase para -a

Coiiio sc piicdc obscrvar cn dichos planos, niiihas estriictiiras conducen a sistemas inestables; sin embargo, el SMC tiene la capacidad de que, aunque las estructuras del sistemas sean inestables, se puede garantizar estabilidad para el sistema combinado (el SMC se puede aplicar, no importando el tipo de estructura, ya sean estables o inestables).

La ley de control permite lograr estabilidad aún cuando para cada estructura el sistema no lo sea. El sistema estará cambiando de una estructura a otra de manera que se llegue ai punto de equilibrio, el sistema conmuta tomando en cuenta, en este caso, dos superficies, XI = O y a = O.

El plano de fase asociado al movimiento con el SMC propuesto es mostrado en la figura 3.5. En cualquier punto de operación en el que se encuentre el sistema, el control aplicará un estado tal que obligue al sistema a llegar y permanecer en a; una vez ahí el sistema es llevado al punto de equilibrio, en este caso cero.

40

Figura 3.5 Plano de fase con el SMC.

Coli base lo anterioi del SMC, los pasos dc discfio puedcii scr enlistados 1141:

Obtener el modelo del sistema. Proponer una superficie de deslizamiento. Verificar la existencia del modo deslizante. Verificar la estabilidad dentro de la superficie.

3.3. Modelo del sistema

3.3.1. Diagrama esquemático

El diagrama esquemático de la topología propuesta se muestra en la figura 3.6, el pie-regulador, como ya sc iiiciicioiió, es iiiia topología dciioiiiiiiada como Rcdiictor de Armónicos [ i l l , el cual corrige el FP, debido a que es un Convertidor Elevador bidireccional en corriente. Asitnisino el regulador es un convertidor Flyback.

Figura 3.6 Diagrama esquemático completo de la topología propuesta.

3.3.2. Circuito equivalente general

En la figura 3.7 se muestra un circuito equivalente de la topología propuesta; dicho circuito facilita la deducción del modelo matemático del convertidor en variables de estado. El interruptor ideal u1 sustituye los interruptores de estado sólido MI y Mz. Cuando U I 1, M I está encendido y MZ esta apagado, por lo tanto LH se está cargando y cb puede estar proporcionando energía a LF dependiendo de la posición de u2. Si U I = -1, sucede lo contrario, es decir, MI está apagado y M2 está encendido, el capacitor se está cargando/descargando a través de LH y es posible que entregue también energía a LF dependiendo de la posición de LIZ.

41

ESfRA'I'EGIA DI; CONI'ROI,

L,

El interruptor ideal u2 einula al interruptor de estado sólido M j y al transforinador

alniacena energía en la bobina del primario, en esie iiioiiieiito el capacitor dc salida (e,) entrega energía a la carga (R). Si u2 = -1, M3 está apagado y la bobina del secundario carga al capacitor de salida y entrega energía a R.

dcl Convci.tiiloi. I7lyh:ick. Ciliiliilo 11) - 1 sc siiiiill:i <l¡ic M.\ C S I : ~ ciicCii<li i l i) y 1 ~ 1 i . I ( I liiiilo SI:

"I

R

C,==V,,(t) +

Variables de estado son:

x, = vc, ( t ) , xz = i,, (t) > x, = vc, ( t ) > * 4 = 4, (t)

Pero se hace una transformación de manera que se obtiene un modelo mas sencillo.

3.3.3. Modelo mateniático cuando 111 = u2 = 1

Cii'cuiío equivalenie

Según la figura 3.8, MI y M3 están encendidos y Mz esta apagado, por lo tanto C, y V,,(t) entregan la energía que demanda R, además se puede observar que LH se está recargando y que cb le entrega energía a LF.

I I I I I Figura 3.8 Circuito equivalente cuando u, = u2 = 1

Modelo matemático

42

Modelo matemático /ransformado

3.3.4. Modelo matemático cuando u1 = u2 = -1

Circuito equivalente

Se aprecia en la figura 3.9, que MZ esta encendido y que Mi y M3 están apagados, por lo tanto LE, C, y Vi,(t) entregan la energía que demanda R, además se puede apreciar que CI, se está recargando a través de LH.

Figura 3.9 Circuito equivalente cuando ut = u2 = -1 .

Modelo maieináiico

Modelo maiemá/ico transformado

43

ESTRAlEGIA DE CONTROL

donde:

3 . 3 . 5 . Modelo matemático cuando u1 = 1, U 2 = -1

Circuito equivalente

Se puede observar cn la figura 3.10, quc M I y MI cslAii cncciididos y M2 csíú pagado, por lo iaiiito Ch esta dcsconectado. I , I . C,, y V,,,(t) entregan la energía que demanda I<, L I I se está cargando.

+ V,#) c, +

Figura 3.10 Circuito equivalente cuando u , = 1, u2 = - 1

Modelo matemático

Modelo rnalemáfico fransforniado

o o -:, :II:::]+I o o o x,, -"I 17,

o w , - w , o x,, 0 o

3.3.6. Modelo matemático cuando U I = -1, u2 = 1

Circuito equivalente

(3.10)

(3.1 I )

En este caso, según se muestra en la figura 3.1 1, M2 está encendido y Mi y M3 están apagados, por lo tanto cb ~ ' L F se cargan a través de Lii, de tal forma que la energía se pueda utilizar en el momento que C, necesite recargarse. Además en este momento la carga R es alimentada por C, y Vi,,(!), es necesario recalcar que la energía que da V,,(t) no se procesa sino que se entrega directamente a la carga.

44

ESTRATEGIA DE CONTROL

(3.12)

Modelo matemático transformado

3.3.7. Modelo final

Reuniendo los modelos anteriores en uno, encontramos el siguiente modelo matemático final:

o o o - ; w ,

o o o o 0 O o o ;IijLlI + I 2 w I o o o

(3.14)

45

ESTRATEGIA DE CONTROL

donde:

Este modelo tiene la forma:

X = A,X + A,Xu, t A,Xü, + B

Como puede observarse la ecuación (3.14) es no lineal.

(3.14)

3.4. Superficie de deslizainiento

La superficie de deslizamiento (o) propuesta es una combinación lineal de las variables de estado y las referencias [14].

(3.15) . . o = S X - S X , =SeX=O

S = [SI s2 s3 sq]; S I , si, sj y s4 = constantes de diseño, X = [xi x2 x3 ~ 4 1 ~ ; XI, x2, x3 y x4 = variables de estado, X, = [xir ~2~ xjr xdr]’; X I , , ~ 2 ~ , ~3~ y xir = referencias de las variables de estado, eX=[exi ex2 ex3 ex4]”= [xi-xi, x Z - X ~ , X J - X ~ ~ ~ 4 . ~ 4 ~ 1 .

donde:

‘T

Para simplificar cl análisis se disiiiigueii dos supcríiciec dc deslizatiiiciito (ni y 0 2 )

debido a que hay dos convertidores (pre-regulador y regulador). En el análisis de la ley de control UI, se considera que s2 = s3 = O, y para u2 SI = s4 = O, por lo tanto las superficies de deslizamiento son:

paraul:

para u2:

donde:

ol =s,,,x-s,,~x, = S , , , ~ X = S , ( X , - x I r ) t s 4 ( x 4 - X , ~ ) = O

o, =s,,,x-s,,,x, = ~ , , , e ~ = s , ( x , -x2;)+s3(x3 - x , ~ ) = o

(3.16)

(3.17)

s1.4 = [SI 0 0 s4]

s 2 , 3 = [o s2 s3 01

En la teoría del SMC, Utkin [15], se define una herramienta conocida como control equivalente (ueq), esta herramienta es utilizada para conocer el comportamiento del sistema una vez que llega y permanece dentro de la superficie. El ueq es un “promedio” entre los valores. de la ley de control real UN (sólo 1 y - l ) , . djcho control no se implementará físicamente, es un “artificio” matemático que nos ayuda en el análisis [14].

46

ESTRATEGIA DE CONTROL