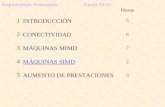

Arquitecturas AvanzadasCurso 10/11 1INTRODUCCIÓN 2CONECTIVIDAD 3MÁQUINAS MIMD 4MÁQUINAS SIMD...

-

Upload

carmelita-lazo -

Category

Documents

-

view

215 -

download

0

Transcript of Arquitecturas AvanzadasCurso 10/11 1INTRODUCCIÓN 2CONECTIVIDAD 3MÁQUINAS MIMD 4MÁQUINAS SIMD...

Arquitecturas Avanzadas Curso 10/11

1 INTRODUCCIÓN

2 CONECTIVIDAD

3 MÁQUINAS MIMD

4 MÁQUINAS SIMD

5 SUPERESCALARES

Horas

5

6

7

2

3

arqAvaTemario Superes-2

6 AUMENTO DE PRESTACIONES

1 Límites de las arquitecturas escalares “Pipeline”

2 Visión global de una arquitectura Superescalar

3 Flujo de instrucciones

4 Flujo de datos en registros

5 Flujo de datos en memoria

6 Microarquitectura del Pentium II, III y 4

7 Microarquitectura del Core 2

8 Microarquitectura del Itanium (IA64)Bibliografía:

“Modern Processor Design. Fundamentals of Superscalar Processors”J. P. Shen y M. H. Lipasti McGraw-Hill-2004 [Caps. 4 y 5]

arqAva Límites de las arquitecturas escalares “Pipeline”Superes-3

d

Aplicable a:

• Instrucciones

• Aritmética

• Acceso a memoria

¡ Todas las instrucciones siguen mismo camino a la misma marcha, salvo parones !

¡ Demasiado rígido !

• Límite superior IPC=1=CPI• Unificación ineficiente en un único pipeline• Pérdida de eficiencia por ejecución tan “en orden”

¿Alcanzable?

arqAva Límite superior IPC=1=CPI ¿Realidad? Superes-4

¿ Qué rendimiento se espera ?

dn, dn-1,..., d2, d1 d’n, d’n-1,..., d’2, d’1

k etapas

SinPipeline

k

Sk =T1

Tk

=n k

(k+n–1) n k

k+n–1=

Lim Sk = kn

¿ Es ésto tan bueno ?

• Límites tecnológicos: k (2..15..); < 10

• k => n

• 1987 – Agerwala y Cocke => CPI ≈ 1,77 .. 1,15

arqAva Límite superior IPC=1=CPI ¿Realidad? Superes-5

Necesario n45para eficiencia 90%

Necesario n89para eficiencia 90%

0

2

4

6

8

10

0 50 100 150

k=6

k=10

SK

n

Aceleración como función de ‘k’ y ‘n’n k

k+n–1Sk =

¿Puedo alimentar el pipe con tantas instrucciones

seguidas?

¡ Saltos !1 cada 5/6 Inst.Predicción OK => 90% ¿Conclusión?

arqAva Unificación ineficiente en un único pipeline Superes-6

F D I E W

Operaciones: ALU + Load/Store

WF D I E E

Operaciones: Coma flotante, Coma fija (mul,div) => Multiciclos

Unificación imposible o muy ineficiente

F D I E E M W

WF D I E M

Prog. ejemplo

r1 = M[Y]

M[X] = r3

r2 = M[Z]

r3 = r1+r2

r4 = M[B]

r5 = M[C]

r6 = r4*r5

M[A] = r6

1 2 3 4 5 6 7 8 9 1011 121314151617181920212223242526

I1I2I3I4I5I6I7I8

arqAva Ejecución “en orden” ineficiente Superes-7

F D I E E EW

F D I E E EW

F DRAW

— — — I E E EW

F ?— — — D ?— — — I E E EW

F

— — —

— — —

— — —

I E E EWD

F I E E EWD

F I E E EWD

F D — — — I E E EW

F D I EE WE

¿Es necesario retener a I5, I6, … ?

¡ Permitir ejecución fuera de orden !

I2I3I4I5I8 I7 I6

arqAva Ejecución “en orden” ineficiente Superes-8

Programa ejemploI1: r1 = M[Y]

I4: M[X] = r3

I2: r2 = M[Z]

I3: r3 = r1+r2

I5: r4 = M[B]

I6: r5 = M[C]

I7: r6 = r4*r5

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

I8: M[A] = r6

19

F D

F D

I

I

E

E

E

E

E

E

W

W

F D I E E E W— ——

F D I — —— —— E E E W

?F D I E E E W

F D I E E E W

F D I — —— E E E W

F D I E E E W— —— — —

Permitiendo ejecución fuera de orden: 26 a 19 ciclos

arqAva Visión global … (Escalar => Superescalar) Superes-9

• Romper límite IPC=1

Pipelines paralelos

IF

ID

RD

ALU

MEM

WB

Grado = 3

• Paralelismo temporal y espacial

• Coste hw adicional:S2 Crossbar entre etapasAccesos paralelos Reg y Cache

• ¿Rendimiento IPC?

2 0,6..1,454 1 .. 26 1,2..2,3

ObservadoUnos 1,58..8Otros 51..90

Teórico

Pentium4 Core2 Itanium PowerG5 3 4 6 8

arqAva Visión global … (Escalar => Superescalar) Superes-10

Benchmark IPC 0 Fetch

bzip2 1,36 14,3

eon 1,24 16,4

gap 1,32 10,4

gcc 1,14 12,2

gzip 1,08 19,6

parser 0,89 25,3

perlbmk 1,10 42,2

Media INT 1,16 20,1

Benchmark IPC 0 Fetch

ammp 1,11 43,2

apsi 1,12 45,1

equake 1,05 39,2

mesa 1,31 21,4

wupwise 1,84 19,7

Media FP 1,29 33,7

• ¿Rendimiento IPC?

2 0,6..1,454 1 .. 26 1,2..2,3

Observado

Simulación con:• PTLsim/X arquitectura tipo x86-64 grado 4• SPEC CPU2006• 200 millones de instrucciones simuladas: datos “Fetch”

arqAva Visión global … (Escalar => Superescalar) Superes-11

• Evitar unificación ineficiente

Pipelines diversificados

IF

ID

RD

WB

ALU MEM1 FP1 BR

MEM2 FP2

FP3

EX

• Diseño adhoc + eficiente: Mejor latencia Menos hardware

• Control cauces EX: Distribuido e independiente

• ¿Cuánta diversidad?

1965 CDC660010

1990 M8811010

1995 Pentium 2

2000 Itanium23

2006 Core 2 Duo14

arqAva Visión global … (Escalar => Superescalar) Superes-12

• Permitir ejecución fuera de orden => Pipelines dinámicos

IF

ID

RD

WB

ALU MEM1 FP1 BR

MEM2 FP2

FP3

EX

Dispatch buffer

Reorder buffer

en orden

en orden

fuera de orden

arqAva Visión global … (Modelo Superescalar) Superes-13

Extraer

Buffer de instrucciones

Decodificar

Despachar

Ejecutar

Completar

Retirar

Buffer de dispatch

Buffer de issuing

Buffer de completar

Buffer de store

Cada instrucción a U.F. adecuada

Forzar terminación en orden

Optimizar acceso a memoria

• ¡ La etapa Fetch no es trivial ! (Caché simple “línea = 4 Inst.”)

CACHE

I

WE

F DWE

WE

WE

4 4

sub add xor sub

rol mul add mov

or bra --- ---

--- add call ---

--- --- sub lsl add load asr sub

para etapa D guardar

add load --- --- --- --- --- ---

--- asr subBuffer

add loadasr subpara etapa D

• Caché extendida “línea = 8 Inst.”

8

arqAva Visión global … (Etapa Fetch) Superes-14

• Caché autoalineada

--- --- sub lsladd load asr sub

PCBancos de memoria

0 1 2 3

sub lsl add load

• ¡ Mucho trabajo !• Identificar las instrucciones concretas y su tipo• Detectar dependencias con instrucciones cercanas• Identificar saltos• Leer operandos

arqAva Visión global … (Etapa Decodificación) Superes-15

RISC lo facilita mucho

• ¿Acelerar? => Predecodificación (parcial) previa [miss cacheI]

Cache

IF D

4 4Memoria

principal

Lógica

Pre

Deco.

Inst1 Inst2 Inst4Inst3 Inst1

4b

Inst2

4b

Inst3

4b

Inst4

4bSaltosIndependencia

Tiene su sobrecarga

arqAva Visión global … (Etapa Despachar) Superes-16

Extraer

Decodificar

Despachar

ALU MEM1 FP1 BR

MEM2 FP2

FP3

Reorder buffer “Completar”

• Decidir a qué U.F. enviar cada instrucción• Transición centralizado a distribuído• Buffer de espera operando(s) no disponible(s)

I5: r4 = M[B]

I6: r5 = M[C]

I7: r6 = r4*r5I7

I6

I5

Estación de reserva

Tomasulocentral

ALU MEM1 FP1 BR

MEM2 FP2

FP3

distribuidas

dispatch

issue

arqAva Visión global … (Etapa Ejecutar) Superes-17

• Tendencia a diversificar más => más U.F. más especializadas

ALU TI SuperSPARC FPU IBM RS/6000

• Salto

• Load / Store

• Multimedia

(a+e+1) + (b+f+1) + 2 2(c+g+1) + (d+h+1) 2 2

• ¿Cuántas U.F. de qué tipo?% TipoInstrucciones

402040 load/store

saltosALU

Regla 4 / 2 / 44

• U.F. > Grado• O(N2)

arqAva Visión global … (Etapa Ejecutar) Superes-18

Bench ld st salto

bzip2 17,4 7,7 11,5

eon 21,3 16,4 8,6

gap 24,4 10,5 13,4

gcc 21,1 10,8 15,2

gzip 17,1 7,7 8,6

parser 24,3 9,2 12,8

perlbmk 23,2 12,0 15,4

INT 21,3 10,6 12,2

Bench ld st salto

ammp 21,1 6,4 7,6

apsi 23,2 5,3 6,6

equake 18,4 8,7 7,2

mesa 23,3 10,8 9,0

wupwise 22,2 10,5 10,1

FP 21,6 8,3 8,1

Simulación con:• PTLsim/X arquitectura tipo x86-64 grado 4• SPEC CPU2006• 200 millones de instrucciones simuladas: datos “Commit”

% TipoInstrucciones

402040 load/store

saltosALU

• ¿Cuántas U.F. de qué tipo?

arqAva Visión global … (Etapas Completar y Retirar) Superes-19

Excepciones precisas

Estado máquina

Prioridad a load vs store

Estado memoria

E X E CC U O T R I E O N

B A C KE N D

F R O N T E N D

?1: r0=r1-r2

2: r3=r4/r0

3:r5=r5+#1

arqAva Flujo de instrucciones (Problemática de los saltos) Superes-20

Programa ejemploI1: r1 = M[A]I2: r3 = r3-1I3: beq I5I4: r2 = r2+r4I5: r5 = r5-r6I6: M[B] = r5

F D E W

• Por simplicidad:

I1: r1 = M[A]

I4: r2 = r2+r4

I2: r3 = r3-1

I3: beq I5

I5: r5 = r5-r6

I5: r5 = r5-r6

1 2 3 4 5 6 7 8

F D E W

I6: M[B] = r5

F D E W

F D E W

F D E W

9 10

F D E W

F D E W

F D E W

! Hasta fin ciclo 5 no se sabe dirección del

salto !

¿Cómo afecta a nuestro modelo?

I1, I2, I3, I4, I5, I5, I6vs

I1, I2, I3, I5, I6

arqAva Flujo de instrucciones (Penalización por saltos) Superes-21

• Incondicionales: bra 28(PC) => Determinar dirección destino• Condicionales: beq 55(R5) => + Evaluar condición de saltar

salto

¿ Perder siempre 3 ciclos ?

21 Instrucciones

Modo dedireccionamiento

• bra 28(PC)

desp(PC)

• bra (R5)(Ri)

desp(Ri)

• bra 55(R5)

?

arqAva Flujo de instrucciones (Penalización por saltos) Superes-22

• Incondicionales: bra 28(PC) => Determinar dirección destino• Condicionales: beq 55(R5) => + Evaluar condición de saltar

salto

Registro Cond.

¡ Demasiada pérdida !

¿ Flags, Registros ?

Registros generales

arqAva Flujo de instrucciones (Técnicas especulativas) Superes-23

• Predecir (especular)

Dirección del salto

Condición del salto

• Mecanismo para validar acierto o fracaso

• Mecanismo de recuperación ante un fallo

Dir. Inst. Salto Dir. DestinoBranch Target Buffer

$00F5A4: beq 4(PC)

$00F5A4 $00F5AC

CacheInst.

PC

Mux+ Saltar

Historia

0 1

FSMSaltar

TT/T NT/T

TN/T NN/N

T T

T

T

NN

N

N

OK86,8 .. 97,0

• Hit BTB 86,5%• ¿ Aliasing ?

El salto siguesu ejecución

arqAva Flujo de instrucciones (Técnicas especulativas) Superes-24

• Mecanismo de recuperación ante un fallo

a

c

N

inst4

d

T

inst5inst6

¡Etiquetar!

b

inst1inst2inst3

T (tag 01)

02

0303

(tag 02)

(tag 03)

010101

a

b

T

inst1inst2inst3

010101

Retirar éstas

c

N

d

T

inst402

inst5inst6

0303

¡Anular!

e

T

inst7inst8

+ ¡Redirigir!

f

T

inst901

¿ Gestión de etiquetas ?

arqAva Flujo de instrucciones (Técnicas especulativas) Superes-25

PowerPC 604

• BTB dividida en dos• BTAC [64] saltos tomados y 1 ciclo• BHT [512] correctora y 2 ciclos• Actualización en Back-End• Estación de reserva Branch [4]

arqAva Flujo de instrucciones (¿Qué se consigue?) Superes-26

• 2 bits historia y 4K entradas [Hennesy …]

AritméticaEnteraMedia 11%

AritméticaComa flotanteMedia 4%

Más frecuentes los bcc

arqAva Flujo de instrucciones (Otras técnicas especulativas) Super-27

• ¿Cómo mejorar en la condición?

• Más bits de historia• Más saltos recordados• Mejorar la función de predicción

Apenas mejora

• Predictores correlacionadosif (d==0) d = 1;if (d==1) ------

Historia de otros saltos influyen en la predicción del salto actual [globalidad]

• Predictores múltiples: local + global ….

Local 2 bits => 7%Correlacionado => 4%Múltiple => 3%

arqAva Flujo de instrucciones (Otras técnicas especulativas) Super-28

• Algunos problemas del predictor simple con 2 bits de historia:

Sea un patrón de salto => T N T N T N T N T………

PC

Historia

0 0

NN/N

T

NT/T

1

¿Guardar dos+ comportamientos?

PC

Historia

1 0 1 0

1 1Registro histórico

de saltos con desplazamiento

0 1 0 1 0 0

¿Cuántos? Idealmente uno por saltoTT/T

TN

TN/T

50%

arqAva Flujo de instrucciones (Otras técnicas especulativas) Super-29

• Algunos problemas del predictor simple con 2 bits de historia:

2 instrucciones distintas y mismo patrón de saltos => ¡Aliasing!

PC

Historia

1 0 1 0

1 11 0 1 0

$A350 bne 4(PC)

$B684 beq 8(PC)

0 0

¿Guardar dos+ historias?

arqAva Flujo de instrucciones (Otras técnicas especulativas) Super-30

• 1992 Yeh y Patt => Predictor adaptativo de dos niveles

PC

• G Global [1]• P Individual [varios]

Adaptativo

• g Global [1]• p Individual [1 * bcc]• s Shared [n * bcc]

GAg, PAg, PAs 90% 95..97%

PentiumPro

arqAva Flujo de instrucciones (Otras técnicas especulativas) Super-31

• 1993 Scott McFarling => Predictor gshare

DEC Alpha 21264

• ISCA’04 Ayosé Falcon y … => Prophet/Critic hybrid branch predictor

Además:Return

AddressStack

arqAva Flujo de instrucciones (Otras técnicas especulativas) Super-32

Bench Hit

bzip2 95,9

eon 93,3

gap 96,0

gcc 92,6

gzip 92,2

parser 99,9

perlbmk 98,8

INT 95,5

Bench salto

ammp 98,9

apsi 99,3

equake 92,3

mesa 97,8

wupwise 97,7

FP 97,2

Simulación con:• PTLsim/X arquitectura tipo x86-64: bimodal(2)+Gshare• SPEC CPU2006• 200 millones de instrucciones simuladas: cond, indir, ret

GAg, PAg, PAs 90% 95..97%

arqAva Flujo de datos en registros Superes-33

EN DESARROLLO

arqAva Flujo de datos en memoria Superes-34

• Problemática del acceso a memoria

ld r2,35(r1)

$000F3A8D

$000F3A58r1

disponible r1

000F3 3F25

TLB

1

$3F25A8D

¿ st r3,20(r4) ?

arqAva Flujo de datos en memoria Superes-35

• ¿Ejecución en orden de los accesos a memoria?

Y(i) = A * X(i) + Y(i)

F0 LD,a R4 ADDI,Rx,#512 ;last addressLoop: F2 LD,0(Rx) ;load X(i)

F2 MULTD,F0,F2 ;A*X(i)

F4 LD,0(Ry) ;load Y(i)

F4 ADDD,F2,F4 ;A*X(i)+Y(i)

0(Ry) SD,F4 ;store into Y(i)

Rx ADDI,Rx,#8 ;inc. index to X

Ry ADDI,Ry,#8 ;inc. Index to Y

R20 SUB,R4,Rx ;compute bound

BNZ,R20,Loop ;check if done

DAXPY :: LINPAC

LD

MULTD

ld, multd, ld, addd, sd ld, multd, ld, addd, sd1ª iteración 2ª iteración

LD

SD

ADDD

¿Fuera de orden?

36

Store X

Store Y

Load Z

Load bypassing

Store X

Store Y

Load X

Load forwarding

• Load Bypassing, Load Forwarding y colas LSQ

L1D

STQ

?

st

arqAva Flujo de datos en memoria Superes-36

LDQ

ldSTQ

• Tag con menos bits “aliassing”

reissue

• Forwarding Tag Addr completa

• Predictor de dependencia LdSt

11..19% 1..4% Mejoras

37

• Load Bypassing, Load Forwarding y colas LSQ [Completo]

arqAva Flujo de datos en memoria Superes-37

STQ

LDQ

arqAva Flujo de datos en memoria Superes-38

Bench fwd

bzip2 12,0

eon 15,4

gap 7,5

gcc 10,0

gzip 10,2

parser 8,0

perlbmk 8,3

INT 10,2

Bench fwd

ammp 1,4

apsi 5,5

equake 12,7

mesa 9,5

wupwise 5,0

FP 6,8

Simulación con:• PTLsim/X arquitectura tipo x86-64: LSQ [LQ.48+SQ.32]• SPEC CPU2006• 200 millones de instrucciones simuladas

• ¿Cuánto forwarding?

arqAva Flujo de datos en memoria Superes-39

• Cache con dos puertos y no bloqueante

• Puede reducir el 15% de la penalización por fallo de cache

¡Contienda!

¿Especulativo?

arqAva Flujo de datos en memoria Superes-40

• Cache con prefetch

•LdAddr•ValueAddrAn

t•Stride2Ant

arqAva Microarquitectura del Pentium II (1) Superes-41

• Busca compatibilidad a nivel ISA (Instruction Set Architecture) con versiones anteriores

• Máquina de origen CISC: Difícil utilización de recursos arquitecturales RISC y superescalares

• Solución: Capa superior CISC y capa inferior ~ RISC

Caché deinstrucciones

Caché de datos

Búsqueda y deco.

de instrucciones

Unidad deejecución

Unidad deafianzamiento

Buffer de reordenación

Caché deNivel 2

Bus

Etapa 1 Fetch

Etapa 2 Fetch

Etapa 3 Fetch

Etapa 1 decodificación

Etapa 2 decodificación

Asignación de registros

Caché deinstrucciones

Buffer de reordenación2

Secuenciadormicroinst. RISC

Predicción dinámicade salto

Predicción estáticade salto

Puntero de instrucciones

Mantiene el flujode instrucciones

Mantiene el flujode instrucciones

Decodifica y determinalongitud de instrucciones Decodifica y determinalongitud de instrucciones

Alinea las instruccionesAlinea las instrucciones

Convierte instrucciones CISCen microinstrucciones RISC

Convierte instrucciones CISCen microinstrucciones RISC

Ordena lasmicroinstrucciones

Ordena lasmicroinstrucciones

Mapea los 16 registrosCISC sobre 40 registros RISC

Mapea los 16 registrosCISC sobre 40 registros RISC

128 bits

6 x 118 bits

3 x 118 bits

128 bits

128 bits

3 x 118 bits

arqAva Microarquitectura del Pentium II (2) Superes-42

Con Exe y WB2

11 etapas

Etapa 1 de decodificaciónSequenciador de

Microinstrucciones RISC

6 x 118 bits

Decodificador 0 Instrucciones complejas

Decodificador 1 Instrucciones simples

Hasta 4microinstrucciones RISC

Hasta 4microinstrucciones RISC

Decodificador 2 Instrucciones simples

Una sólamicroinstrucción RISC

Una sólamicroinstrucción RISC

arqAva Microarquitectura del Pentium II (3) Superes-43

ALU Compleja

ALU MMXMultiplicador

MMXUnidad coma

flotante compleja

Buffer de reordenación

Unidad de Ejecución (Estación de Reserva)Puerto 0 Puerto 1 Puerto 2 Puerto 3 Puerto 4

Unidad dealmacenamiento

Unidad de carga

Unidad comaflotante simple

ALU MMX

DesplazadorMMX

ALU simple yrecuperación saltos

Caché de datosAfianzamiento

Finalización en orden

Data forwarding

Desechar ejecución especulativa

arqAva Microarquitectura del Pentium II (4) Superes-44

Unidad dealmacenamiento

Puerto 5

Unidad SSE

Pentium III

¿Pentium 4?• 20 etapas• Caché de traza

arqAva Microarquitectura del Pentium II (5) Superes-45

• Evolución del pipeline:

Busq Dec1 Dec2 Ejec Escr Pentium1 2 3 4 5

Bus1 Bus2 Bus3 Dec1 Dec2 Aloj Reor Prep Ejec Esc1 Esc2

1 2 3 4 5 6 7 8 9 10 11

Pentium Pro

Bus1 IP Tra1 Tra2 Env1 Aloj Ren1 Ren2 Enc Reo1 Reo2 Reo3 Emi1 Emi2 Lec1 Lec2 Ejec Flag Esc Env2

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

CISC RISC

Pentium 4Dependencias de Datos

¿Intel Core 2? 14

¿ Tejas 45 etapas y 7 Ghz ?nunca

¡ Pentium 4 Prescott 31 etapas !2004

Cache de Trazas

TC

• Cache de trazas del Pentium 4

L1-I Convencional

arqAva Microarquitectura del Pentium II (6) Superes-46

PC

GeneraTrazas

Fallo

arqAva Microarquitectura del Intel Core [..Nehalem]Superes-47

• 14 etapas

• 4 x ciclo

• Sin cache de trazas

• LSQ

Eficiencia energética

www.intel.com

arqAva Microarquitectura del Intel Core Superes-48

• Incremento del rendimiento SSE

arqAva Microarquitectura del Intel Core Superes-49

• Incremento del rendimiento en Prefetch de L1 Datos

Siguiente línead, d+k, d+2k, …

arqAva Microarquitectura del Intel Core Superes-50

• Incremento del rendimiento: Micro-Fusion

add eax,[mem32]

load reg1,[mem32]add reg2,reg1

x86

µOp

add reg1,[mem32]

SuperµOp

cmp eax,[mem32]jne target

x86

cmpjne eax,[mem32],target

µOp

+ Macro-Fusion

10%

5%

15%

arqAva Microarquitectura del Intel Core Superes-51

• Intel Turbo Boost Technology

www.intel.com

Vigilando: Núcleos activos, consumo, temperatura

arqAva Microarquitectura del Intel Core Superes-52

• Intel Enhanced Dynamic Acceleration Technology www.intel.com

• Ahorro gasto snoopy [30%]

¡ Nuevo Diseño ! IA32 => IA64-ItaniumarqAva Microarquitectura del Itanium Superes-53

DualCore

¡ Nuevo Diseño ! IA32 => IA64-ItaniumarqAva Microarquitectura del Itanium Superes-54

¿Un éxito?

¿ Retrasado a 2010 o abandonado ?

arqAva Microarquitectura del Itanium (¿Éxito?) Superes-55

7/12/2005: “Itanium: A cautionary tale” www.news.com

1,7 millones x86

Topt500 Nov/2009

6

AMD x86_64La puntilla

EM64T

22/12/2009: “Red Hat will drop the Itanic” www.theinquirer.net27/05/2009: “Nehalem-EX is 8-core …, likely to signal end of line for Itanium” geek

• L1 2*16KB Latencia 1

• L2 256KB Latencia 5..7

• L3 ..24MB Latencia 14..17

• Superescalar de grado 6

• 23 unidades funcionales: 6 ALU, 6 MALU,

2+2Mem, 3 Salto, 2+2FPU

• Muchos registros (328):

128 Enteros (64+1 “NaT” bits)

128 Coma Flotante (82 bits)

8 Saltos (64 bits)

64 Predicados (1 bit)

• Pipeline de 8 etapas

• DirVir 64bits y DirReal 50bits

1700 mill. Transis. 24MB

3.692$

L3 L2

L1I

L1D

1,6GHz128

arqAva Itanium 2 Superes-56

Dual y Quad Core

Montecito

¿Límites al ILP?

• Complejidad de la planificación dinámica (Hw)

Explicitly Parallel Instruction Computer

• Saltos => Dependencias, Errores de predicción

Ejecución predicada (PREDICATION) Predicción

• Latencia de memoria ¡ Muy lenta !

Cargas especulativas

Todo junto =>? Mejora del 79%

arqAva Itanium: Límites al ILP Superes-57

FIN

Código fuente original

Código

reordenado

Código máquina secuencialCompilador Hardware

Paraleliza

Varias U.F.

U.F. desaprovechadas

Los procesadores frecuentemente están el 60% desocupados

?

arqAva Itanium: complejidad planificación dinámica Superes-58

• Paralelismo Explícito (EPIC)

Código fuente original

Hardware Varias U.F.

U.F. más aprovechadas

Se incrementa la ejecución paralela

Compilador(paraleliza)

Código máquina paralelo

Ventana más

grande

?

arqAva Itanium: EPIC Superes-59

• Paralelismo Explícito (EPIC + VLIW)

Instrucciones agrupadas en fardos (bundle) de 3 en 3

Instrucción 2 Instrucción 1 Instrucción 0 Temp S41 41 41 4 1

Instrucción 2 Instrucción 1 Instrucción 0 Temp S41 41 41 4 1

Se pueden encadenar:

Escalabilidad en cuanto al número de U.F.

arqAva Itanium: EPIC + VLIW Superes-60

Op PRi R1 R2 R314 6 7 7 7

• Ejecución predicada (IF – THEN – ELSE; NEXT)

p1,p2 cmp

Cond

P1=1

P2=0

P1=0

P2=1

T F

P1

P1

P1

P2

P2

P2

Arquitectura tradicional

cmp

THEN

ELSE

IF

NEXT

IA64

Permite eliminar saltos

(difíciles de predecir)

arqAva Itanium: Predication (1) Superes-61

Ejecución Afianzamiento

Ejecución con resultados

afirmados mediante <Prj>

Ejecución con resultados

afirmados mediante <Prj>

Ejecución con resultados

afirmados mediante <Pri>

Ejecución con resultados

afirmados mediante <Pri>

V1 := V1 + 1

V2 := V2 / 2

V3 := V3 * 3

V4 := V4 - 4

V5 := V5 + 1

V6 := V6 - 1

a AND ba AND ba AND b

T F

arqAva Itanium: Predication (2) Superes-62

Pr1, Pr2 := Condición

<Pr1> Pr1, Pr2 := Condición

V1 := V1 + 1;

IF (a AND b) THEN

BEGIN

V2 := V2 / 2;

V3 := V3 * 3;

END;

ELSE

BEGIN

V4 := V4 - 4;

V5 := V5 + 5;

END;

V6 := V6 - 6;

add RV1, #1

cmp a, #0 --false

beq Else

cmp b, #0 --false

beq Else

div RV2, #2

mul RV3, #3

bra FinIf

Else sub RV4, #4

add RV5, #5

FinIf sub RV6, #6

add RV1, #1

Pr1, Pr2 := cmp (a = 0)

<Pr2> Pr1, Pr2 := cmp (b = 0)

<Pr2> div RV2, #2

<Pr2> mul RV3, #3

<Pr1> sub RV4, #4

<Pr1> add RV5, #5

sub RV6, #6

Mezcladas

arqAva Itanium: Predication (3) Superes-63

• Carga de datos de memoria antes de que se necesiten

• Disminuye el impacto que genera la alta latencia de las memorias

• Se intenta adelantar las cargas lo máximo posible.

Problema:Puede que la carga

no sea necesariaPuede que la carga

no sea necesaria

Puede que se provoqueuna falta de página

Puede que se provoqueuna falta de página

ld.s R2, (Dir2)

<Pr2> chk.s R2

Solución: Separar la carga de

la posible excepción generada

t1 = t1 + 1if t1 > t2 j = a[t1 – t2] j++

add t1 + 1

comp t1 > t2

jump

load r8, a[t1-t2]

add r8 + 1

barrera

add t1 + 1

ld.s r8=a[t1-t2]

comp t1 > t2

jump

check.s r8

add r8 + 1

arqAva Itanium: Cargas Especulativas Superes-64